# Power Engineering Letters

## Fast Convergence Delayed Signal Cancellation Method for Sequence Component Separation

Roberto Cárdenas, Senior Member, IEEE, Matías Díaz, Felix Rojas, and Jon Clare, Senior Member, IEEE

Abstract—Delayed signal cancellation is one of the methods used to separate the negative- and positive-sequence components in unbalanced  $3\phi$  systems. In this letter, a DSC methodology with fast convergence time is proposed and it is shown that an improved separation of the positive and negative sequences is feasible. Experimental results are presented to demonstrate the performance of the proposed methodology.

*Index Terms*—Control systems, delay signal cancellation, symmetrical components.

#### I. INTRODUCTION

**I** N SEVERAL applications, it is necessary to obtain the negative- and positive-sequence components of voltage and current signals. Typical examples are control systems for low-voltage ride through (LVRT) [1], flicker mitigation [2], and phase-locked-loop (PLL) implementations [3], [4], etc.

Conventional DSC methods reported in the literature separate the positive- and negative-sequence components using

$$\underline{\hat{v}}_{1\alpha\beta} = \frac{1}{2} \left[ \underline{v}_T(t) - j\underline{v}_T\left(t - \frac{T}{4}\right) \right] \tag{1}$$

$$\underline{\hat{v}}_{2\alpha\beta} = \frac{1}{2} \left[ \underline{v}_T(t) + j\underline{v}_T\left(t - \frac{T}{4}\right) \right]$$

(2)

where  $\underline{\hat{v}}_{1\alpha\beta}, \underline{\hat{v}}_{2\alpha\beta}$  are estimations of the positive- and negativesequence signals, respectively;  $\underline{v}_T$  is the total voltage vector; and T is the signal period. The main disadvantage of using (1)–(2) is that a significant delay (5 ms for 50 Hz) is created in the result. In addition, in digital implementations, the ratio  $T/(4T_s)$  (where  $T_s$  is the sampling period) has to be an integer,

Manuscript received February 21, 2014; revised August 17, 2014; accepted November 06, 2014. Date of publication November 20, 2014; date of current version July 21, 2015. This work was supported in part by Fondecyt Chile under Grant 1140337 and in part by the Advanced Center for Electrical and Electronic Engineering, Basal Project FB0008. Paper no. PESL-00101-2014.

R. Cárdenas and M. Díaz are with the Electrical Engineering Department, University of Chile, Santiago, Chile (e-mail: rcd@ieee.org).

F. Rojas is with the Technical University of Munich, Munich 80339, Germany (e-mail: felix.rojas@tum.de).

J. Clare is with the Faculty of Engineering, University of Nottingham, Nottingham University Park NG7 2RD, U.K. (e-mail: Jon.Clare@nottingham.ac. uk).

Color versions of one or more of the figures in this paper are available online at http://ieeexplore.ieee.org.

Digital Object Identifier 10.1109/TPWRD.2014.2373038

which is not always feasible [2]. Moreover, another disadvantage of (1)–(2) is that a relatively large number of memory positions could be required to store the vector  $\underline{v}_T(t-T/4)$ . In this paper, a DSC methodology with a reduced settling time is proposed for the separation of sequence components.

Conventional DSC methods, as well as the fast settling method presented in this paper, are affected by harmonic distortion in the signals [2]. Filtering has to be applied before using (1) and (2) [3] or a complex generalized DSC (which has high computational burden) has to be implemented [4]. The filtering or preprocessing stage is considered outside the scope of this paper. Therefore, in this paper, it is assumed that the signals at the DSC input have reduced harmonic distortion. Hence, the voltage vector  $\underline{v}_T$  is composed of positive- and negative-sequence components as shown

$$\underline{v}_T = v_1 e^{j\omega t + \emptyset_1} + v_2 e^{-j\omega t + \emptyset_2}.$$

(3)

Then, using (3), it can be shown that the positive- and negativesequence signals can be obtained as

$$\underline{\hat{v}}_{1\alpha\beta} = \frac{1}{2} \left[ \underline{v}_T(t) - \frac{j}{\omega} \frac{\partial \underline{v}_T(t)}{\partial t} \right]$$

(4)

$$\underline{\hat{v}}_{2\alpha\beta} = \frac{1}{2} \left[ \underline{v}_T(t) + \frac{j}{\omega} \frac{\partial \underline{v}_T(t)}{\partial t} \right].$$

(5)

It is well known that in a digital implementation, direct differentiation of the voltage amplifies the noise in  $\underline{v}_T$ . Therefore, an alternative is to use the following expression:

$$\underline{v}_s = \underline{v}_T(\omega t) - e^{-j\theta_d} \underline{v}_T(\omega t - \theta_d)$$

(6)

where  $\theta_d$  is the delay angle. In an experimental implementation, this angle is calculated as  $\theta_d = 2\pi T/(NT_s)$ , where N is an integer. Using (3) in (6) (assuming  $\emptyset_1 = \emptyset_2 = 0$ ), the vector  $\underline{v}_s$ is obtained as

$$\underline{v}_s = v_1 e^{j\omega t} + v_2 e^{-j\omega t} - e^{-j\theta_d} \left[ v_1 e^{j(\omega t - \theta_d)} + v_2 e^{-j(\omega t - \theta_d)} \right]$$

(7)

By simple inspection of (6)–(7), it is concluded that the negative-sequence component is cancelled, yielding

$$\frac{\hat{\underline{v}}_{1\alpha\beta}}{\left[1-e^{-j2\theta_d}\right]} = \frac{1}{2} \frac{\left[\underline{v}_T(\omega t) - e^{-j\theta_d} \underline{v}_T(\omega t - \theta_d)\right] (1 - e^{j2\theta_d})}{\left[1 - 2\cos(2\theta_d)\right]} \quad (8)$$

0885-8977 © 2014 IEEE. Personal use is permitted, but republication/redistribution requires IEEE permission. See http://www.ieee.org/publications\_standards/publications/rights/index.html for more information.

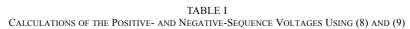

$$\hat{v}_{1\alpha} = \frac{(v_{\alpha T} - v_{\alpha T}^{\theta_d} \cos \theta_d - v_{\beta T}^{\theta_d} \sin \theta_d - (v_{\alpha T} - v_{\alpha T}^{\theta_d} \cos \theta_d - v_{\beta T}^{\theta_d} \sin \theta_d) \cos 2\theta_d + (v_{\beta T} - v_{\beta T}^{\theta_d} \cos \theta_d + v_{\alpha T}^{\theta_d} \sin \theta_d) \sin 2\theta_d)}{2(1 - \cos 2\theta_d)}$$

$$\hat{v}_{1\beta} = \frac{(v_{\beta T} - v_{\beta T}^{\theta_d} \cos \theta_d + v_{\alpha T}^{\theta_d} \sin \theta_d - (v_{\beta T} - v_{\beta T}^{\theta_d} \cos \theta_d + v_{\alpha T}^{\theta_d} \sin \theta_d) \cos 2\theta_d - (v_{\alpha T} - v_{\alpha T}^{\theta_d} \cos \theta_d - v_{\beta T}^{\theta_d} \sin \theta_d) \sin 2\theta_d)}{2(1 - \cos 2\theta_d)}$$

$$\hat{v}_{2\alpha} = \frac{(v_{\alpha T} - v_{\alpha T}^{\theta_d} \cos \theta_d + v_{\beta T}^{\theta_d} \sin \theta_d - (v_{\alpha T} - v_{\alpha T}^{\theta_d} \cos \theta_d + v_{\beta T}^{\theta_d} \sin \theta_d) \cos 2\theta_d + (v_{\beta T} - v_{\alpha T}^{\theta_d} \cos \theta_d - v_{\alpha T}^{\theta_d} \sin \theta_d) \sin 2\theta_d)}{2(1 - \cos 2\theta_d)}$$

$$\hat{v}_{2\beta} = \frac{(v_{\beta T} - v_{\beta T}^{\theta_d} \cos \theta_d - v_{\alpha T}^{\theta_d} \sin \theta_d - (v_{\beta T} - v_{\beta T}^{\theta_d} \cos \theta_d - v_{\alpha T}^{\theta_d} \sin \theta_d) \cos 2\theta_d - (v_{\alpha T} - v_{\alpha T}^{\theta_d} \cos \theta_d + v_{\beta T}^{\theta_d} \sin \theta_d) \sin 2\theta_d)}{2(1 - \cos 2\theta_d)}$$

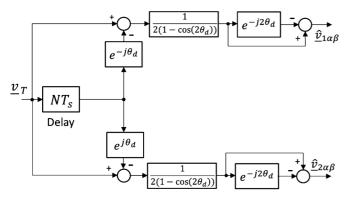

Fig. 1. Proposed fast DSC.

where  $\hat{v}_{1\alpha\beta}$  is an estimation of the positive-sequence signal. The negative-sequence component of the signal is estimated by using

$$\underline{\hat{v}}_{2\alpha\beta} = \frac{1}{2} \frac{\left[\underline{v}_T(\omega t) - e^{j\theta_d} \underline{v}_T(\omega t - \theta_d)\right] (1 - e^{-j2\theta_d})}{\left[1 - 2\cos(2\theta_d)\right]}.$$

(9)

It can be shown that (8) and (9) are equivalent to (4)–(5) when  $\theta_d \rightarrow 0$ . Using (8) and (9), the implementation of the proposed fast DSC is shown in Fig. 1. The time delay of  $NT_s$  seconds corresponds to a delay angle of  $\theta_d$  rads. Using  $\theta_d = \pi/2$ , the conventional DSC of (1) and (2) is obtained. Notice that the use of  $\theta_d > \pi/2$  is also possible, which could be an alternative for sequence separation with very noisy signals (i.e., delays > 5 ms).

Using Fig. 1 and (8) and (9), the estimation (in the  $\alpha$ - $\beta$  frame) of the sequence components can be obtained using the equations shown in Table I. For compactness,  $\underline{v}_T^{\theta_d}$  stands for  $\underline{v}_T(\omega t - \theta_d)$  and the subscripts "1", "2" stand for the positive and negative sequence, respectively. Notice that N samples of the signal  $\underline{v}_T(t)$  have to be stored in the digital processor memory for the implementation of this fast convergence DSC algorithm.

#### **II. EXPERIMENTAL IMPLEMENTATION**

The fast DSC algorithm proposed in this paper has been experimentally tested. A TMS320C6713 DSP augmented with a field-programmable gate-array (FPGA) board has been used to estimate the sequence components using the equations given in Table I. A data-acquisition system with a sampling frequency of 10 kHz is used in this application. Three Hall-effect voltage transducers are used to measure the grid voltages. A programmable AMETEK power source is used to generate type

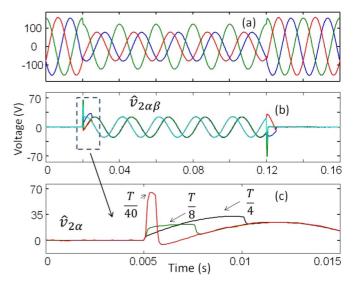

Fig. 2. Experimental results. (a)  $v_{\alpha n}, v_{b n}$  and  $v_{c n}$  for a dip D grid fault. (b)  $\alpha -\beta$  negative-sequence components. (c) Amplified view of (b) for  $\hat{v}_{2\alpha}$ .

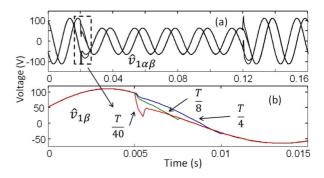

Fig. 3. (a)  $\alpha - \beta$  positive-sequence components corresponding to the test shown in Fig. 2(a). (b) Amplified view of (a) for  $\hat{v}_{1\beta}$ .

D voltage dips. The output of this power source is regulated to 110-V<sub>rms</sub> at 50 Hz.

In the DSP implementation, the proposed fast DSC has been programmed with delays (in parallel) of T/4 (conventional DSC [2]), T/8, and T/40 (T = 20 ms). Fig. 2 shows the experimental results for a voltage dip of type D. As shown in Fig. 2(a), at t  $\approx$ 20-ms voltages,  $v_{an}$  and  $v_{cn}$  decrease by 50% and  $v_{bn}$  decreases by 75% of their previous values. In Fig. 2(b), the estimated negative-sequence voltages are shown. Notice the relatively high peak achieved by the T/40 estimation. This is produced by the numerical implementation of  $(\partial \underline{v}(t)/\partial t)$  using a 500- $\mu$ s time delay [see (9)]. Fig. 2(c) shows an amplified view of the dip. Notice that the conventional DSC takes 5 ms to converge to the correct negative-sequence voltage. The T/40DSC converges very quickly within 500  $\mu$ s (five samples). Fig. 3(a) shows the estimation of the positive-sequence component for the voltages depicted in Fig. 2(a). In Fig. 3(b), an amplified view [corresponding to the dashed box of Fig. 3(a)] of  $\hat{v}_{1\beta}$  is shown. Again, the convergence is very fast for a delay time of T/40. The estimator with a delay time of T/8 settles down in  $\approx 2.5$  ms with reduced overshoot. Therefore, for a given application, a compromise between the minimum value of  $\theta_d$ , the noise level, and the maximum overshoot allowed can be reached.

### III. CONCLUSION

An improved DSC method with a fast settling time has been proposed in this paper. The implementation is based on the equations given in Table I. Unlike the conventional methodology, the proposed DSC can estimate the positive/negative-sequence signals within a small fraction of a cycle. For instance in this paper, the method has been tested for  $\theta_d < 9^\circ$  (500  $\mu$ s) with good performance. As anticipated from (4)–(5) for smaller values of  $\theta_d$ , more noise and overshoot are expected because the numerical implementation of  $\partial \underline{v}(t)/\partial t$  is implicit in (8) and (9). Therefore, for a particular application, a compromise between noise, overshoot, and minimum  $\theta_d$  value has to be reached.

#### REFERENCES

- D. Ramirez, S. Martinez, C. A. Platero, F. Blazquez, and R. M. de Castro, "Low-voltage ride-through capability for wind generators based on dynamic voltage restorers," *IEEE Trans. Energy Convers.*, vol. 26, no. 1, pp. 195–203, Mar. 2011.

- [2] J. Svensson, M. Bongiorno, S. Member, and A. Sannino, "Practical implementation of delayed signal cancellation method for phase-sequence separation," *IEEE Trans. Power Del.*, vol. 22, no. 1, pp. 18–26, Jan. 2007.

- [3] J. C. Alfonso-Gil, J. J. Vague-Cardona, S. Orts-Grau, F. J. Gimeno-Sales, and S. Seguí-Chilet, "Enhanced grid fundamental positive-sequence digital synchronization structure," *IEEE Trans. Power Del.*, vol. 28, no. 1, pp. 226–234, Jan. 2013.

- [4] Y. F. Wang and Y. W. Li, "Grid synchronization PLL based on cascaded delayed signal cancellation," *IEEE Trans. Power Electron.*, vol. 26, no. 7, pp. 1987–1997, Jul. 2011.