PAPER

# Unipolar resistive switching behavior in $Al_2O_3/HfO_2$ multilayer dielectric stacks: fabrication, characterization and simulation

To cite this article: M Maestro-Izquierdo et al 2020 Nanotechnology 31 135202

View the article online for updates and enhancements.

# **Recent citations**

- Numerical Study of Graphene Heat Spreaders for a THz Quantum Diode Based on a G-MGIM Junction E. Moreno *et al*

# IOP ebooks<sup>™</sup>

Bringing together innovative digital publishing with leading authors from the global scientific community.

Start exploring the collection-download the first chapter of every title for free.

Nanotechnology 31 (2020) 135202 (10pp)

# Unipolar resistive switching behavior in Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> multilayer dielectric stacks: fabrication, characterization and simulation

# M Maestro-Izquierdo<sup>1</sup>, M B Gonzalez<sup>1</sup>, F Jimenez-Molinos<sup>2</sup>, E Moreno<sup>3</sup>, J B Roldan<sup>2</sup> and F Campabadal<sup>1</sup>

<sup>1</sup> Institut de Microelectrònica de Barcelona, IMB-CNM, CSIC, Carrer dels Til·lers s/n, Campus UAB. E-08193 Bellaterra, Spain

<sup>2</sup> Departamento de Electrónica y Tecnología de Computadores, Universidad de Granada, Facultad de Ciencias. Avenida Fuentenueva s/n, E-18071 Granada, Spain

<sup>3</sup> Departamento de Ingeniería Eléctrica, Universidad de Chile, Avenida Tupper 2007, Santiago de Chile, Chile

E-mail: marcos.maestro@csic.es

Received 5 July 2019, revised 31 October 2019 Accepted for publication 6 December 2019 Published 9 January 2020

# Abstract

In this work, the impact of different  $HfO_2/Al_2O_3$ -based multilayer dielectric stack (DS) configurations on the electrical characteristics and on the resistive switching (RS) performance of Ni/Insulator/Silicon devices has been systematically investigated. Significant differences are observed in the electrical characteristics of the fabricated bilayer, trilayer and pentalayer stacks compared to a single  $HfO_2$  layer of the same physical thickness. The RS analysis has shown similar low resistance state currents and set voltages for all the DS combinations whereas currents at the high resistance state and reset voltages depend on the DS. The shift of the reset voltage to lower values for  $HfO_2$  and  $Al_2O_3/HfO_2/Al_2O_3$  cases is explained by the results from thermal simulations that reveal that these differences could be associated to the different temperature distributions at the narrowest part of the conductive filament immediately before the thermally triggered reset process occurs.

Supplementary material for this article is available online

Keywords: ALD, HfO<sub>2</sub>, Al<sub>2</sub>O<sub>3</sub>, resistive switching, multilayer dielectric stacks, thermal simulations, nanolaminates

(Some figures may appear in colour only in the online journal)

# 1. Introduction

Devices based on the resistive switching (RS) phenomenon are currently being investigated for applications such as nonvolatile resistive random access memories [1], synapses in neuromorphic computing [2, 3] or physical unclonable functions for security applications [4, 5]. Among the possible alternatives, RS devices based on HfO<sub>2</sub> have shown fast switching times, high endurance, low energy consumptions, CMOS compatibility, and an excellent capability to modulate their electrical resistance [3, 6]. In addition, several works [7–14] have shown the advantage of using HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack combinations in RS devices to enhance their electrical properties. For instance, Azzaz *et al* [7], have published the improvement of the device endurance and data retention when a thin layer of  $Al_2O_3$  is added to a single HfO<sub>2</sub> layer. Yu *et al* [8], have demonstrated an improved multilevel capability of HfO<sub>x</sub>/AlO<sub>x</sub> bilayer stacks under DC and AC conditions. Furthermore,  $Al_2O_3/HfO_2/Al_2O_3$  trilayer stacks have been reported to have excellent RS performances with low parameter dispersion [9] and an improved multilevel cell operation by controlling reset stop voltages and good switching characteristics under AC condition [10]. Besides that, other groups have demonstrated RS behavior and performance improvements in  $HfO_2/Al_2O_3$  multilayers employing more than three layers. Among them, Tzeng *et al* [11] have reported both positive and negative unipolar RS behavior of  $HfO_2/Al_2O_3$ -based multilayers observing differences in switching and stability characteristics between the two operation modes. In addition, Huang *et al* [12] implemented  $HfO_2/Al_2O_3$  multilayer stacks in RRAM arrays showing an improved tail-bit retention compared to single layer  $HfO_2RRAM$ .

This work is focused on unipolar RS devices with Ni as metal electrode where the high temperature on the reset process due to joule heating is the most predominant cause for the rupture of the conductive filament (CF) [15]. Notice that Ni migration in the dielectric, facilitates the formation of metallic filaments, which is thermally and voltage induced [16]. In [13], Tran *et al* reported in unipolar Ni-based RRAM devices a reduced switching variability and an increased resistance ratio between two states when using a HfO<sub>x</sub>/AlO<sub>y</sub> bilayer stack compared to a single HfO<sub>x</sub> layer. The order of a HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> bilayer, however, was reported to have no impact on Ni-based RRAM characteristics [14].

Although some studies have dealt with the RS behavior in HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> multilayer dielectric stacks (DS), no performance comparisons in an extended set of several multilayer stack configurations have been reported, being difficult to isolate the contribution of the DS on the device performance from the contribution of the other processing steps in the fabrication process. Thus, in this work, unipolar RS devices with Ni top electrode and bilayer, trilayer and multilayer (pentalayer) DS combining and alternating HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> layers have been fabricated and systematically characterized to study in depth the impact of different dielectric configurations on the electrical characteristics and on the RS performance. In addition, the experimental results are combined with physical simulation to further understand the role of the DS on the device performance. To this end, the capacitance-voltage and current-voltage characteristics have been first measured and analyzed. Then, a RS assessment of all DS has been carried out, including the analysis of the cycle-to-cycle variability. Finally, combining the experimental RS results and analysis together with thermal simulations of the devices, the thermal response of the fabricated structures has been studied. In this respect, a comprehensive investigation on the thermal behavior is done making use of a simulation tool that solves the 3D heat equation in a detailed manner.

### 2. Device fabrication

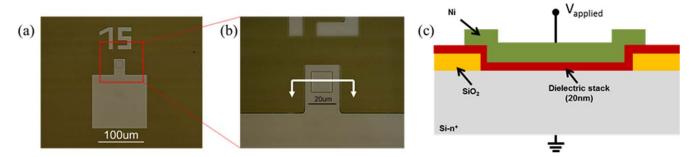

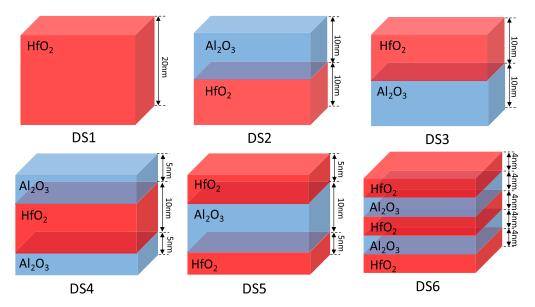

The fabricated metal–insulator–semiconductor (MIS) devices are field-oxide isolated Ni/insulator/Si-n<sup>+</sup> square structures with active areas ranging from 480 × 480 to 5 × 5  $\mu$ m<sup>2</sup>. A cross sectional view is shown in figure 1. The devices were fabricated on highly doped n-type (100) Czochralski silicon wafers with a resistivity in the range (0.007–0.013)  $\Omega$  cm. After a standard wafer cleaning, a 200 nm thick SiO<sub>2</sub> layer was grown by means of a wet thermal oxidation process at 1100 °C. This field oxide was patterned by photolithography and wet etching. Prior to insulator deposition, a cleaning in  $H_2O_2/H_2SO_4$  and a dip in HF(5%) were done. The oxide layers were grown at 225 °C by atomic layer deposition (ALD) in a Cambridge NanoTech Savannah 200 system. The precursors used were trimethylaluminium, (TMA) and  $H_2O$  for  $Al_2O_3$ , and tetrakis(dimethylamido)-hafnium (TDMAH) and  $H_2O$  for HfO<sub>2</sub>. N<sub>2</sub> was employed as carrier and purge gas. Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub> layers were combined to build bilayer, trilayer and pentalayer DS all of them with a total physical thickness of 20 nm. Samples with a 20 nm thick HfO<sub>2</sub> layer were also fabricated for comparison purposes. Figure 2 shows the studied DS combinations referred to as DS1 to DS6. The top metal electrode of the fabricated devices consists of a 200 nm thick Ni layer deposited by magnetron sputtering and patterned by a lift-off process.

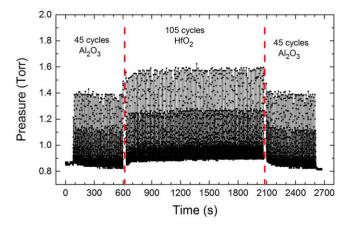

The ALD technique provides excellent thickness control and uniformity. The oxide thickness can be obtained by adjusting the number of ALD cycles [17] to grow a HfO<sub>2</sub> layer of 20, 10, 5 or 4 nm, the ALD consisted in 210, 105, 55 and 36 ALD cycles. Analogously, 91, 45 and 36 ALD cycles were used to grow Al<sub>2</sub>O<sub>3</sub> layers of 10, 5 and 4 nm, respectively. An example of the ALD reactor pressure in the deposition process carried out to obtain the trilayer DS (5 nm-Al<sub>2</sub>O<sub>3</sub>/10 nm-HfO<sub>2</sub>/5 nm-Al<sub>2</sub>O<sub>3</sub>) is shown in figure 3.

TEM inspections of 20 nm thick  $HfO_2$  layers indicate that they are polycrystalline [18], while ALD grown  $Al_2O_3$  films are amorphous.

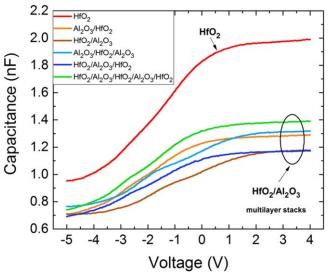

# 3. Impact of the multilayer stack on the electrical characteristics and dielectric reliability

A first electrical characterization of the fabricated MIS devices was performed through the measurement and analysis of the high-frequency capacitance–voltage (*C*–*V*) characteristics. In order to obtain reliable capacitance measurements, devices with an area of 480 × 480  $\mu$ m<sup>2</sup> were used. The *C*–*V* measurements were carried out at 100 kHz signal frequency by sweeping the voltage from inversion to accumulation using an HP4192A impedance analyzer in parallel configuration. Figure 4 shows representative *C*–*V* characteristics of the studied DS. From the experimental *C*–*V* curves, the equivalent oxide thickness (EOT), defined as the required thickness of a silicon dioxide film to achieve the same capacitance density as the high-*k* material [19], was extracted for the different DS from the following equation:

$$C_{\max,\text{high-}k} = \frac{\varepsilon_0 k_{\text{SiO}_2}}{\text{EOT}} A,$$

(1)

where  $C_{\text{max}}$  is the maximum capacitance measured at the accumulation region,  $\varepsilon_0$  the vacuum permittivity,  $k_{\text{SiO2}}$  the relative dielectric constant of SiO<sub>2</sub>, and *A* the capacitor area. From equation (1), for a high-*k* layer of physical thickness  $t_{\text{high-}k}$ , EOT is related to it by the following relationship:

$$EOT = \frac{k_{SiO_2}}{k_{high-k}} t_{high-k}.$$

(2)

Figure 1. Optical image of (a) the top view of a fabricated MIS device and (b) zoom of the active area. (c) Schematic cross section of the device along the white line indicated in (b).

Figure 2. Fabricated HfO<sub>2</sub> and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>-based dielectric stacks (DS) combinations labeled from DS1 to DS6.

Figure 3. Reactor pressure of the atomic layer deposition (ALD) process for the 5 nm- $Al_2O_3/10$  nm- $HfO_2/5$  nm- $Al_2O_3$  trilayer stack.

**Figure 4.** *C*–*V* characteristics at 100 kHz for the different dielectric stack combinations. Device area is  $480 \times 480 \ \mu m^2$ .

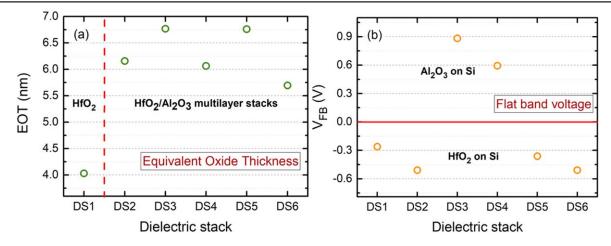

Figure 5. Extracted (a) equivalent oxide thickness (EOT) and (b) flat band voltage ( $V_{\rm FB}$ ) parameters from the high-frequency C-V characteristics.

In figure 5(a), where the obtained values for EOT are depicted for the different stacks, it is shown that the inclusion of Al<sub>2</sub>O<sub>3</sub> in a multilayer stack leads to larger EOT values compared to a single HfO<sub>2</sub> layer. Considering equation (2), this result is in accordance with the lower dielectric constant of Al<sub>2</sub>O<sub>3</sub> (~9) compared to HfO<sub>2</sub> (~25). Notice that all the stacks have a physical thickness of 20 nm. In addition, in the case of multilayer stacks, similar EOT values were obtained for the different combinations; the smallest one corresponds to the pentalayer stack (DS6 split). This result is due to the fact that, in this case, the thickness ratio  $t_{\rm HfO_2}/t_{\rm Al_2O_3}$  is 3/2, while in the other cases the ratio is 1.

In addition, from the experimental C-V curves, the flat band voltage ( $V_{\rm FB}$ ) was determined from the flat band capacitance ( $C_{\rm FB}$ ) and considering the series connection of the oxide capacitance ( $C_{\rm ox}$ ) and the flat band semiconductor capacitance.  $C_{\rm FB}$  [20] is then given by:

$$C_{\rm FB} = \frac{A}{\frac{A}{C_{\rm or}} + \frac{L_{\rm D}}{\varepsilon_{\rm r}}},\tag{3}$$

where  $L_D$  is the Debye length,  $\varepsilon_s$  is the silicon dielectric constant and A the device area. The extracted  $V_{FB}$  values, shown in figure 5(b), indicate that for those DS with an Al<sub>2</sub>O<sub>3</sub> layer adjacent to the silicon substrate (DS3: HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and D6: Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>)  $V_{FB}$  is positive whereas for those with a HfO<sub>2</sub> layer deposited on the silicon substrate  $V_{FB}$  is negative. This result is consistent with the larger fixed negative charge reported in Al<sub>2</sub>O<sub>3</sub> layers compared to HfO<sub>2</sub> [21]. This fixed negative charge in Al<sub>2</sub>O<sub>3</sub> films can be attributed to Al vacancies, O interstitials, and interstitial H, because of the H containing ALD precursors TMA (Al(CH<sub>3</sub>)<sub>3</sub>) and H<sub>2</sub>O [22]. In addition, the presence of fixed negative charge in Al<sub>2</sub>O<sub>3</sub> layer has also been reported to be influenced by *C*-related impurities [23].

With respect to assessing the electrical conduction through the different DS, current–voltage (*I–V*) measurements were performed using an HP4155 semiconductor parameter analyzer on pristine devices with an area of  $15 \times 15 \ \mu m^2$ . The voltage was applied to the Ni top electrode, while the Si substrate was grounded. Voltage sweeps

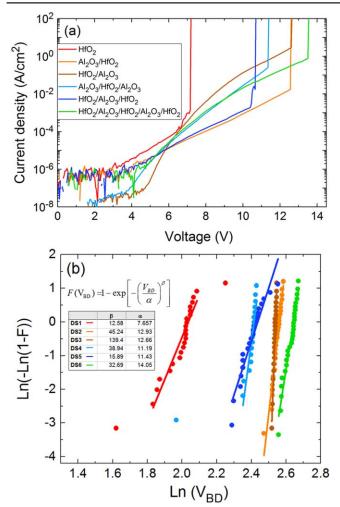

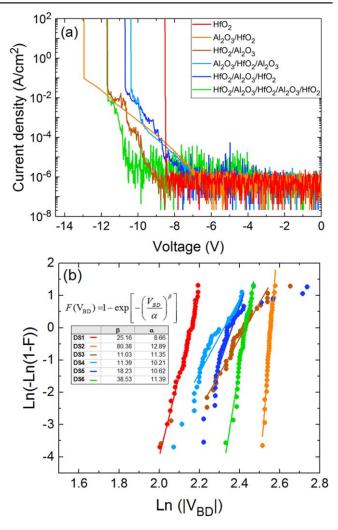

were applied from 0 V up to the occurrence of the dielectric breakdown for both polarities. Since these type of devices need to be subjected to a forming process before the RS phenomenon is observed, the obtained I-V characteristics are representative of the forming behavior of the studied devices in both polarities. Figures 6(a) and 7(a) show typical I-V curves for each DS under substrate (positive bias) and gate (negative bias) injection regimes, respectively. Under substrate injection (figure 6(a)), devices with a single HfO<sub>2</sub> layer exhibit larger currents than multilayer stacks at voltages values below  $\sim 7 \text{ V}$  (figure 6(a)). This fact could be related to the lower conduction band offset (barrier height) between the silicon substrate and the insulator layer in the case of HfO<sub>2</sub>  $(\sim 1.4 \text{ eV})$  case than in Al<sub>2</sub>O<sub>3</sub>  $(\sim 2.5 \text{ eV})$  [24]. For larger voltages (>7 V), the  $HfO_2/Al_2O_3$  stack presents the largest current while Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> stacks show the smallest. This difference is in accordance with the work carried out in [14], where the dielectric conduction in  $Al_2O_3/HfO_2$  and  $HfO_2/Al_2O_3$  bilayer stacks was compared. Under gate injection (figure 7(a)), no dielectric conduction is observed in any stack for voltage values below |-7 V|. However, at larger voltages, higher current values are observed for the trilayer cases in comparison to the other multilayer stacks.

Comparing the current behavior at large voltages ( $\sim$ 8 V) independently of the injection regime, stacks with Al<sub>2</sub>O<sub>3</sub> adjacent to the injecting electrode show larger current than those having HfO<sub>2</sub>. The explanation of such a result is given by the analysis of the band diagram carried out for every multilayered stack. In the case of the Al<sub>2</sub>O<sub>3</sub> layer located next to the injecting electrode and the device positively or negatively biased, electrons only find an Al<sub>2</sub>O<sub>3</sub> barrier with triangular shape and once overcome no further barrier is found and, therefore, larger conduction is possible. However, when  $HfO_2$  is the adjacent layer, electrons encounter two barriers the first due to the HfO<sub>2</sub> layer and the second to the contiguous Al<sub>2</sub>O<sub>3</sub> layer, since Al<sub>2</sub>O<sub>3</sub> has a larger bandgap (8.7 eV) than HfO<sub>2</sub> (5.7 eV). Notice that this double  $HfO_2/Al_2O_3$  barrier can be double triangular shaped or even a combination of a trapezoidal and a triangular shape

**Figure 6.** (a) Current–voltage characteristics for positive bias (substrate injection) up to dielectric breakdown. (b) Weibull plot of the cumulative breakdown distribution function *F* versus breakdown voltage,  $V_{\rm BD}$  in *V*. The extracted shape ( $\beta$ ) and scale ( $\alpha$ ) parameters of the Weibull function for the different dielectric stacks are shown in the inset table. Device area is 15 × 15  $\mu$ m<sup>2</sup>.

what makes the conduction more difficult and leads to a lower current.

In order to evaluate the reliability of  $HfO_2/Al_2O_3$  multilayer stacks compared to a single  $HfO_2$  layer, the dielectric breakdown has been studied. For this purpose, ramped *I–V* characteristics of a set of more than 25 capacitors of each type and for each polarity were measured and the breakdown voltage ( $V_{BD}$ ) was recorded. Comparison of the obtained results is carried out through the analysis of the Weibull cumulative breakdown distributions (figures 6(b) and 7(b)) defined as:

$$F(V_{\rm BD}) = 1 - \exp\left[-\left(\frac{|V_{\rm BD}|}{\alpha}\right)^{\beta}\right],\tag{4}$$

where  $\alpha$  is the voltage at which 63.2% of the capacitors are broken, and  $\beta$  is the Weibull slope, which indicates the width of the distribution. The obtained  $\alpha$  and  $\beta$  values are shown in the inset table of figure 6(b) (positive polarity) and figure 7(b) (negative polarity). It can be noticed that for both polarities

M Maestro-Izquierdo et al

**Figure 7.** (a) Current–voltage characteristics for negative bias (top electrode injection) up to dielectric breakdown. (b) Weibull plot of the cumulative breakdown distribution function *F* versus |breakdown voltage| ( $V_{BD}$  in *V*). The extracted shape ( $\beta$ ) and scale ( $\alpha$ ) parameters of the Weibull function for the different dielectric stacks are shown in the inset table. Device area is 15 × 15  $\mu$ m<sup>2</sup>.

the lowest breakdown voltage corresponds to the single  $HfO_2$ layer compared to multi-layered dielectrics (figures 6(a) and 7(a)), resulting in a significantly smaller  $\alpha$  parameter. In addition, among the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> stack combinations, both trilayer stacks show the lowest  $\alpha$  parameter under both polarities, while the  $\beta$  parameter shows no clear trend.

The analysis of the electrical characteristics and dielectric reliability in pristine devices have demonstrated the different physical properties of the fabricated multilayered stacks. These results confirm that prior to the forming process, the insulator films show dissimilar capacitance and conduction behavior.

# 4. Effect of the DS on the RS phenomenon

Having observed significant differences in the electrical characteristics of the different stacks, RS behavior is next studied in order to analyze the impact of the type of stack on

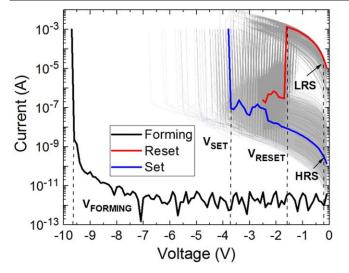

**Figure 8.** Experimental *I–V* curves for the forming process and 2000 cycles of negative unipolar RS for the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stack. HRS, LRS,  $V_{\text{FORMING}}$ ,  $V_{\text{SET}}$  and  $V_{\text{RESET}}$  parameters are indicated. Device area is 5 × 5  $\mu$ m<sup>2</sup>.

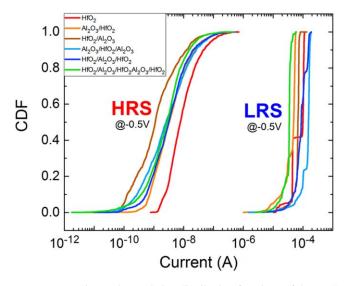

**Figure 9.** Experimental cumulative distribution functions of the HRS and LRS currents, extracted at -0.5 V, corresponding to a set of 2000 RS cycles.

the RS performance. Previous works on Ni-based devices with a single  $HfO_2$  layer [25–27] reported better RS performance under negative unipolar conditions in comparison to other polarity combinations. Under such conditions, by applying negative voltage ramps, a metallic-like CF is formed (set process) and disrupted (reset process) [28]. According to [15, 27], the formation of the CF is due to metallic diffusion through the oxide layer from the top electrode into the dielectric, while the disruption of CF is known to be a temperature-driven rupture of the filament [2, 29–31].

### 4.1. RS assessment

In order to study the negative unipolar RS performance of the devices, as the first and necessary step, they were subjected to a forming process under negative polarity with a current

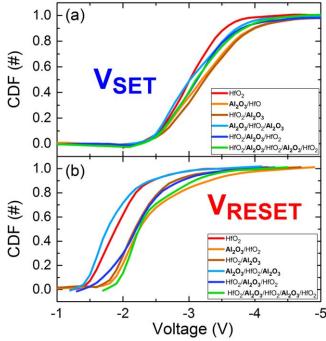

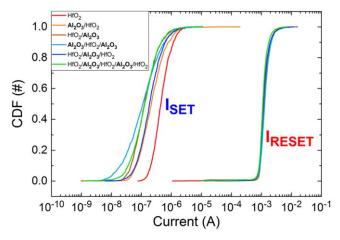

**Figure 10.** Experimental (a) set and (b) reset voltage cumulative distribution functions obtained from 2000 RS cycles for each of the different dielectric stacks.

**Figure 11.** Experimental cumulative distribution functions of the set and reset currents obtained from 2000 RS cycles for each of the different dielectric stacks.

limitation of 1 mA in order to form the CF but preventing the hard and irreversible dielectric breakdown. In our previous work [32], it was shown that the CF is most likely to be created within the active area of the device rather than at the edge. With the purpose of reducing the variability of the switching process, devices with an area of  $5 \times 5 \ \mu m^2$  were used. Then, 2000 consecutive reset-set cycles were performed applying negative voltage sweeps to drive the device to the high resistance state (HRS) and to the low resistance state (LRS), alternatively. It should be noted that in the set processes a current limitation of 1 mA was imposed to prevent hard breakdown whereas the reset process was performed without current limitation. RS measurements were carried out using a B1500 semiconductor parameter analyzer. As an

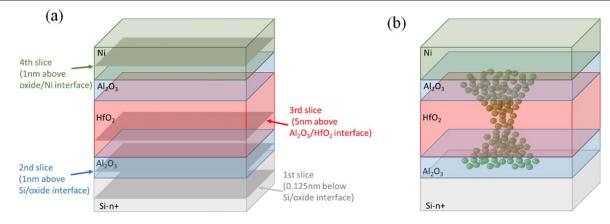

**Figure 12.** (a) Simulation domain of the device under study. The dielectric trilayer  $(Al_2O_3/HfO_2/Al_2O_3)$  stack and electrodes are included; the simulations were performed for the DS4 and DS5 structures. The four slices where the temperature distributions in the cross-sections are considered for the analysis are also indicated. (b) Device structure with a symmetric truncated-cone-shaped CF, as used in the simulation scheme.

example, figure 8 shows the I-V curves of the forming step and the 2000 RS cycles for the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> DS, where characteristic RS parameters such as voltages at which forming, set and reset processes occur,  $V_{\text{FORMING}}$ ,  $V_{\text{SET}}$  and  $V_{\text{RESET}}$ , respectively, and the currents at the HRS and LRS are indicated.

To perform a statistical analysis, the aforementioned parameters were extracted from the 2000 RS cycle measurements for each DS. Figure 9 shows the experimental cumulative distribution functions (CDF) of the HRS and LRS current values, measured at -0.5 V. In the HRS case, the CDF of HfO<sub>2</sub> (red curve) and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> (brown curve) are shifted to slightly larger and lower current values, respectively, in comparison with the other stacks whose CDFs are overlapped. However, in the LRS case, no correlation between the CDF curve and the DS is found. Focusing on curve spreads, similar cycle-to-cycle variability is observed for the different DS for both, HRS and LRS currents. However, larger variability is observed in HRS with respect to LRS. This larger variability is attributed to the variation of the gap distance in the filamentary path after each reset process.

Figure 10 shows CDFs of the extracted set and reset voltages ( $V_{\text{SET}}$ ,  $V_{\text{RESET}}$ ). For both voltages, a similar variability is observed for the different DS combinations. However, whereas an overlapping of V<sub>SET</sub> CDF curves is observed, two different clear trends can be noticed in the case of the V<sub>RESET</sub> CDF curves. First, the HfO<sub>2</sub> (red curve) and Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> (soft blue curve) stacks show lower values than the other stacks, with reset voltage distributions shifted  $\sim -0.5$  V. In addition, the CDFs of the current values at  $V_{\text{SET}}$  and  $V_{\text{RESET}}$ ,  $I_{\text{SET}}$  and  $I_{\text{RESET}}$ , respectively, are depicted in figure 11. It is remarkable that CDF curves of IRESET values clearly overlap for all DS while ISET CDF curves slightly differ among each other, being the stack with a single HfO<sub>2</sub> (red curve) layer the one with the largest values of  $I_{SET}$ . Notice that for the single HfO<sub>2</sub>, the HRS current is also slightly larger (see figure 9).

From this study, we can conclude that although the order and number of layers of  $HfO_2/Al_2O_3$  multilayer stacks strongly influences their electrical properties, in terms of RS performance the main parameter that shows a clear dependence between the different  $HfO_2/Al_2O_3$  multilayers stack combinations is the reset voltage. In order to shed some light on this issue thermal simulations are presented in the next section.

### 4.2. Analysis of the temperature distributions along CF

Focusing on the results obtained in figure 10, where the reset distribution of HfO2 and Al2O3/HfO2/Al2O3 stacks are shifted  $\sim -0.5$  V from the rest of stacks, the impact of the DS on the reset voltage is studied using a simulation tool that solves the 3D heat equation [33-35]. This numerical procedure is in line with other works related to the study of thermal effects in RRAM devices [36-39]. Previously published results [34], showed that Ni-based devices with a single layer of aluminum oxide had higher reset voltages and lower temperature distributions than a single HfO<sub>2</sub> layer or  $HfO_2/Al_2O_3$  bilayers. This result is linked to the higher thermal conductivity in Al<sub>2</sub>O<sub>3</sub> ( $k_{th} = 2.86 \text{ W m}^{-1} \text{ K}^{-1}$ ) with respect to HfO<sub>2</sub> ( $k_{th} = 1.0 \text{ W m}^{-1} \text{ K}^{-1}$ ). In the first case, the lateral heat flux from the CF to the oxide is higher and in order to achieve the temperature that triggers the reset process, higher Joule heating effects are needed, therefore a higher reset voltage is expected. In this work, devices with trilayer DS Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> (figure 10) have been studied in terms of temperature distributions. The devices have been analyzed at the LRS considering that Joule heating occurs in the metallic-like CF, which is formed by Ni atom clusters and modeled with cylindrical and truncated-cone shapes. The simulation tool is described in detail in the supplementary material (available online at stacks.iop.org/NANO/31/135202/mmedia) along with the numerical implementation of the 3D heat equation and the algorithm employed to solve it.

Simulations have been performed assuming a device voltage of -1 V and the current is modeled flowing through a fully formed symmetric truncated-cone shaped CF. After the simulations are performed, different temperature distributions

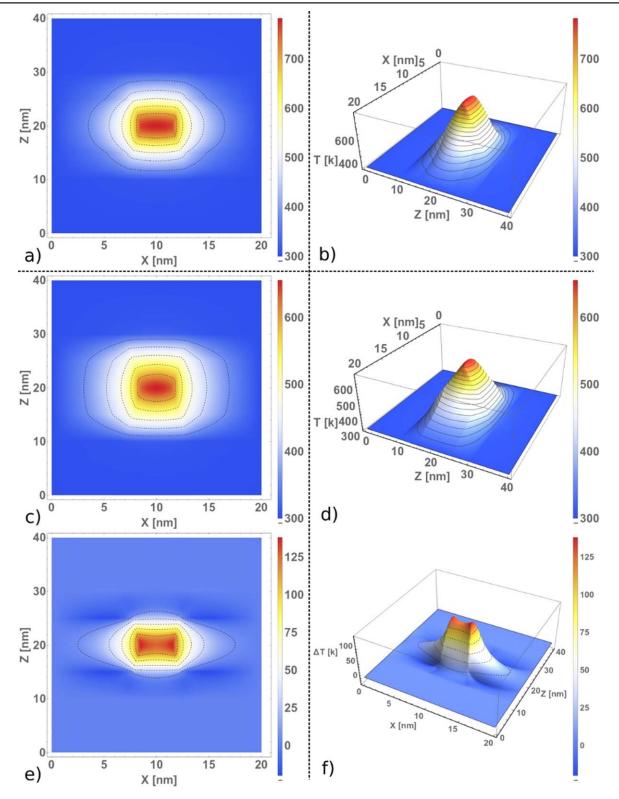

**Figure 13.** Temperature distribution along the vertical direction (*Z* axis, from the Si to the Ni electrodes) for the devices with  $Al_2O_3/HfO_2/Al_2O_3$  (DS4, (a) contour plot, (b) 3D plot) and  $HfO_2/Al_2O_3/HfO_2$  (DS5, (c) contour plot, (d) 3D plot) dielectric stacks. The cross-sections were taken at the middle of the *Y* axis, corresponding to the position where the CF revolution axis is found. The electrode layers included in the simulations are also shown (*Z* axis, Si electrode: 0 < z < 10 nm, and Ni electrode: 30 nm < z < 40 nm). (e) Contour and (f) 3D plots of the subtraction of the temperature distributions shown in (a)–(d).

cross-sections in the 3D simulation domain for the devices under study have been plotted (see the supplementary material). Figure 12(a) shows a sketch of the simulated trilayer DS  $Al_2O_3/HfO_2/Al_2O_3$  (in addition to the electrodes) that constitutes the simulation domain (a similar domain is employed in the DS5 case). The slices (cross-sections) employed to study the temperature distributions are located at the different positions figure 12(a). The electrodes are also taken into consideration in the simulation (10 nm in each electrode layer). The simulations were performed accounting for symmetric CFs with their narrow part placed at the dielectric central region (figure 12(b)). This reasoning was in line with a previous study for devices with single and two dielectrics layers [33, 34].

In figure 13, the temperature distributions along the vertical simulation domain axis, from the Si electrode to the Ni electrode, for Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub> devices are shown. It can be seen that the temperature for the  $Al_2O_3/HfO_2/Al_2O_3$  is higher in the central dielectric region, where the CF narrowing is found, as expected taking into account the lower thermal conductivity of HfO<sub>2</sub> with respect to Al<sub>2</sub>O<sub>3</sub>. Contour and 3D plots are given in this figure (plots (e) and (f) show the temperature difference distribution found between the two types of devices under consideration). The higher temperature in the Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> central dielectric region suggests that the self-accelerated processes linked to RS are triggered in these devices at lower voltages since the structure is thermally more efficient to accumulate the dissipated heat. See also temperatures close to 300 K in the electrodes and in the regions far from the filament, where heat dissipation takes place; this result is coherent from the thermal viewpoint. The simulation results explain, therefore, the experimental results shown above and confirm the influence of temperature on RS mechanisms. The different thermal conduction properties of the materials employed in the DS allow the modulation of the operation temperature within the devices. In doing so, the control of essential operation parameters such as the reset voltage is achieved, facilitating the fabrication of what it could be called thermally engineered devices to lower the power consumption of circuits based on these technologies.

# 5. Conclusions

MIS devices with bilayer, trilayer and pentalayer DS combining and alternating HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> have been fabricated with the aim of studying the impact of the different dielectric configurations on electrical characteristics and the RS performance. The results show larger EOT for HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stacks compared to a single HfO2 layer, because of the lower Al<sub>2</sub>O<sub>3</sub> dielectric constant, and indicate the presence of larger fixed negative charge in the Al<sub>2</sub>O<sub>3</sub> layers. Moreover, a larger breakdown strength under both polarities have been observed for multilayer stacks compared to a single HfO<sub>2</sub> layer. The results from RS analysis have shown relevant dissimilarities in V<sub>RESET</sub> parameters between the fabricated DS combinations.  $V_{\text{RESET}}$  is shifted  $\sim -0.5$  V for the case of single layer HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> compared to the rest of the stacks. In order to shed some light into this issue, thermal simulations have been carried out considering that Joule heating occurs in the metallic-like CF. The results reveal that the differences in  $V_{\text{RESET}}$  values among the stacks could be associated to different temperature distributions at the narrowest part of the CF obtained during the thermally triggered reset process.

# Acknowledgments

The authors thank the support of the Spanish Ministry of Science, Innovation and Universities and the ERDF program through projects TEC2017-84321-C4-1-R, TEC2017-84321-C4-3-R. We also thank the support of FENDECYT project, reference 3180130. This work has made use of the Spanish ICTS Network MICRONANOFABS.

# **ORCID** iDs

- M Maestro-Izquierdo https://orcid.org/0000-0002-8940-9050

- M B Gonzalez https://orcid.org/0000-0001-6792-4556 F Jimenez-Molinos https://orcid.org/0000-0002-8866-7568

- J B Roldan https://orcid.org/0000-0003-1662-6457

- F Campabadal https://orcid.org/0000-0001-7758-4567

# References

- [1] Govoreanu B et al 2011  $10 \times 10 \text{ nm}^2 \text{ Hf/HfO}_r$  crossbar resistive RAM with excellent performance, reliability and low-energy operation Tech. Dig.-Int. Electron Devices Meet. IEDM pp 31.6.1-4

- [2] Ielmini D 2018 Brain-inspired computing with resistive switching memory (RRAM): devices, synapses and neural networks Microelectron. Eng. 190 44-53

- [3] Padovani A, Woo J, Hwang H and Larcher L 2018 Understanding and optimization of Pulsed SET operation in HfOx -based RRAM Devices for neuromorphic computing applications IEEE Electron Device Lett. 39 672-5

- [4] Charles Herder B, Yu M-D, Koushanfar F and Devadas S 2014 F. IEEE, physical unclonable functions and applications: a tutorial Proc. IEEE 102 1126-41

- [5] Arumí D, Gómez-Pau Á, Manich S, Rodríguez-Montañés R, González M B and Campabadal F 2019 Unpredictable bits generation based on rram parallel configuration IEEE Electron Device Lett. 40 341-4

- [6] Poblador S, Gonzalez M B and Campabadal F 2018 Investigation of the multilevel capability of TiN/Ti/HfO<sub>2</sub>/W resistive switching devices by sweep and pulse programming Microelectron. Eng. 187-188 148-53

- [7] Azzaz M et al Improvement of performances HfO2-based RRAM from elementary cell to 16 kb demonstrator by introduction of thin layer of Al<sub>2</sub>O<sub>3</sub> Solid State Electron. 125 2016 182-8

- [8] Yu S, Wu Y, Chai Y, Provine J and Wong H S P 2011 Characterization of switching parameters and multilevel

capability in HfOx/AlOx bi-layer RRAM devices Int. Symp. VLSI Technol. Syst. Appl. Proc. pp 106–7

- [9] Wang L G, Qian X, Cao Y Q, Cao Z Y, Fang G Y, Li A D and Wu D 2015 Excellent resistive switching properties of atomic layer-deposited Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> trilayer structures for non-volatile memory applications *Nanoscale Res. Lett.* **10** 135

- [10] Liu J, Yang H, Ma Z, Chen K, Zhang X, Huang X and Oda S 2018 Characteristics of multilevel storage and switching dynamics in resistive switching cell of Al<sub>2</sub>O<sub>3</sub>/HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> sandwich structure J. Phys. D: Appl. Phys. 51 025102

- Tzeng W-H *et al* 2011 Resistive switching characteristics of multilayered (HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub>)n n = 19 thin film *Thin Solid Films* 520 3415–8

- [12] Huang X, Wu H, Gao B, Sekar D C, Dai L, Kellam M, Bronner G, Deng N and Qian H 2016 HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> multilayer for RRAM arrays: a technique to improve tail-bit retention *Nanotechnology* 27 395201

- [13] Tran X A, Yu H Y, Gao B, Kang J F, Sun X W, Yeo Y-C, Nguyen B Y and Li M F 2011 Ni electrode unipolar resistive RAM performance enhancement by AlOy incorporation into HfOx switching dielectrics *IEEE Electron Device Lett.* 32 1290–2

- [14] Mallol M M, Gonzalez M B and Campabadal F 2017 Impact of the HfO<sub>2</sub>/Al<sub>2</sub>O<sub>3</sub> stacking order on unipolar RRAM devices *Microelectron. Eng.* 178 168–72

- [15] Wu X, Cha D, Bosman M, Raghavan N, Migas D B, Borisenko V E, Zhang X X, Li K and Pey K L 2013 Intrinsic nanofilamentation in resistive switching J. Appl. Phys. 113 114503

- [16] Lee C B et al 2007 Electromigration effect of Ni electrodes on the resistive switching characteristics of NiO thin films Appl. Phys. Lett. 91 082104

- [17] Rafí J M, Zabala M, Beldarrain O and Campabadal F 2011 Deposition temperature and thermal annealing effects on the electrical characteristics of atomic layer deposited Al<sub>2</sub>O<sub>3</sub> films on silicon *J. Electrochem. Soc.* **158** G108

- [18] Martín G 2018 Combined transmission electron microscopy and *in-situ* scanning tunneling microscopy characterization of nanomaterials *PhD Thesis* Universitat de Barcelona 10. 1017/CBO9781107415324.004

- [19] Houssa M 2004 *High-K Gate Dielectrics* (Bristol: IOP Publishing)

- [20] Nicollian E H and Brews J R 2003 MOS (Metal Oxide Semiconductor) Physics And Technology (New York: Wiley-Interscience)

- [21] Campabadal F, Rafí J M, Zabala M, Beldarrain O, Faigón A, Castán H, Gómez A, García H and Dueñas S 2011 Electrical characteristics of metal-insulator-semiconductor structures with atomic layer deposited Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub>, and nanolaminates on different silicon substrates *J. Vac. Sci. Technol.* B 29 01AA07

- [22] Hoex B, Gielis J J H, Van De Sanden M C M and Kessels W M M 2008 On the c–Si surface passivation mechanism by the negative-charge-dielectric Al<sub>2</sub>O<sub>3</sub> J. Appl. Phys. 104 113703

- [23] Jin H S, Kim D H, Kim S K, Wallace R M, Kim J and Park T J 2019 Strategic selection of the oxygen source for low temperature-atomic layer deposition of Al<sub>2</sub>O<sub>3</sub> thin film *Adv*. *Electron. Mater.* 5 1–7

- [24] Peacock P W and Robertson J 2002 Band offsets and Schottky barrier heights of high dielectric constant oxides J. Appl. Phys. 92 4712–21

- [25] Gonzalez M B, Rafi J M, Beldarrain O, Zabala M and Campabadal F 2014 Analysis of the switching variability in

Ni/HfO<sub>2</sub>-based RRAM devices *IEEE Trans. Device Mater. Reliab.* **14** 769–71

- [26] Gonzalez M B, Acero M C, Beldarrain O, Zabala M and Campabadal F Investigation of the resistive switching behavior in Ni/HfO<sub>2</sub>-based RRAM devices 2015 10th Spanish Conf. Electron Devices, IEEE, 2015 pp 1–3

- [27] Rodriguez-Fernandez A, Aldana S, Campabadal F, Sune J, Miranda E, Jimenez-Molinos F, Roldan J B and Gonzalez M B 2017 Resistive switching with Self-Rectifying tunability and influence of the oxide layer thickness in Ni/HfO<sub>2</sub>/n + -Si RRAM devices *IEEE Trans. Electron Devices* 64 3159–66

- [28] Martín G, González M B, Campabadal F, Peiró F, Cornet A and Estradé S 2018 Transmission electron microscopy assessment of conductive-filament formation in Ni–HfO<sub>2</sub>–Si resistive-switching operational devices *Appl. Phys. Express.* **11** 1–4

- [29] Russo U, Ielmini D, Cagli C and Lacaita A L 2009 Selfaccelerated thermal dissolution model for reset programming in unipolar resistive-switching memory (RRAM) devices *IEEE Trans. Electron Devices* 56 193–200

- [30] Russo U, Ielmini D, Cagli C and Lacaita A L 2009 Filament conduction and reset mechanism in NiO–based resistiveswitching memory (RRAM) devices *IEEE Trans. Electron Devices* 56 186–92

- [31] Villena M A, González M B, Roldán J B, Campabadal F, Jiménez-Molinos F, Gómez-Campos F M and Suñé J 2015 An in-depth study of thermal effects in reset transitions in HfO<sub>2</sub> based RRAMs Solid State Electron. 111 47–51

- [32] Claramunt S, Wu Q, Maestro M, Porti M, Gonzalez M B, Martin-Martinez J, Campabadal F and Nafría M 2015 Nonhomogeneous conduction of conductive filaments in Ni/HfO<sub>2</sub>/Si resistive switching structures observed with CAFM *Microelectron. Eng.* 147 335–8

- [33] Villena M A, González M B, Jiménez-Molinos F, Campabadal F, Roldán J B, Suñé J, Romera E and Miranda E 2014 Simulation of thermal reset transitions in resistive switching memories including quantum effects J. Appl. Phys. 115 214504

- [34] Cazorla M, Aldana S, Maestro M, González M B, Campabadal F, Moreno E, Jiménez-Molinos F and Roldán J B 2019 Thermal study of multilayer resistive random access memories based on HfO<sub>2</sub> and Al<sub>2</sub>O<sub>3</sub> oxides *J. Vac. Sci. Technol.* B 37 012204

- [35] Aldana S, García-Fernández P, Rodríguez-Fernández A, Romero-Zaliz R, González M B, Jiménez-Molinos F, Campabadal F, Gómez-Campos F and Roldán J B 2017 A 3D kinetic Monte Carlo simulation study of resistive switching processes in Ni/HfO<sub>2</sub>/Si-n+-based RRAMs *J. Phys. D: Appl. Phys.* **50** 335103

- [36] Wang D-W, Chen W, Zhao W-S, Zhu G-D, Kang K, Gao P, Schutt-Aine J E and Yin W-Y 2019 Fully coupled electrothermal simulation of large RRAM arrays in the 'Thermal-House *IEEE Access.* 7 3897–908

- [37] Li S, Chen W, Luo Y, Hu J, Gao P, Ye J, Kang K, Chen H, Li E and Yin W-Y 2017 Fully coupled multiphysics simulation of crosstalk effect in bipolar resistive random access memory *IEEE Trans. Electron Devices* 64 3647–53

- [38] Sun P, Lu N, Li L, Li Y, Wang H, Lv H, Liu Q, Long S, Liu S and Liu M 2015 Thermal crosstalk in threedimensional RRAM crossbar array *Sci. Rep.* 5 13504

- [39] Lu N, Sun P, Li L, Liu Q, Long S, Hangbing L and Liu M

2016 Thermal effect on endurance performance of

3-dimensional RRAM crossbar array *Chin. Phys.* B 25

056501

10