UNIVERSIDAD DE CHILE FACULTAD DE CIENCIAS FISICAS Y MATEMATICAS DEPARTAMENTO DE INGENIERÍA ELÉCTRICA

# CLOCK-GATING FOR LATCH BASED DESIGNS

## MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA

# JOAQUÍN RUBÉN JESÚS FIGUEROA ÁLVAREZ

PROFESOR GUÍA: VICTOR GRIMBLATT HINZPETER

> SANTIAGO DE CHILE JULIO 2012

UNIVERSIDAD DE CHILE FACULTAD DE CIENCIAS FISICAS Y MATEMATICAS DEPARTAMENTO DE INGENIERÍA ELÉCTRICA

### CLOCK-GATING FOR LATCH BASED DESIGNS

## MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA

JOAQUÍN RUBÉN JESÚS FIGUEROA ÁLVAREZ

PROFESOR GUÍA: VICTOR GRIMBLATT HINZPETER

MIEMBROS DE LA COMISIÓN: HÉCTOR AGUSTO ALEGRÍA NICOLÁS BELTRÁN MATURANA

> SANTIAGO DE CHILE JULIO 2012

RESUMEN DE LA MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA POR: JOAQUÍN RUBÉN JESÚS FIGUEROA ÁLVAREZ FECHA: JULIO 2012 PROF. GUÍA: VICTOR GRIMBLATT HINZPETER

#### **CLOCK-GATING FOR LATCH BASED DESIGNS**

Digital circuits, whose play a crucial role in everyday life, consume large amounts of power which is undesirable as a general rule, and specially for battery power devices such as cellphones, thus circuit designers and automatic synthesis tools aim to reduce power consumption of such circuits using different techniques.

One of the most successful power reduction techniques is clock-gating used in *Flip-Flop* based designs, which aims to reduce the power consumption caused by the transitions in the **clk** signal. The power reduction is achieved by the insertion of clock-gating cells which keeps the **clk** signal of reaching the *Flip-Flops* when they aren't expected to modify their output signal.

Latch based designs being used less that *Flip-Flop* based design and with additional complexities are still largely used for some benefits of the *Latch* timing restrictions, but no automatic synthesis tool provides an automatic clock-gating insertion feature therefore *Latch* based design circuit designers are forced to perform clock-gating by hand which is far from efficient.

The present work focus on clock-gating and the requirements to allow its use in *Latch* based designs from the automatic synthesis tool perspective, while providing theoretical discussion on the differences between *Latches* and *Flip-Flops* and how these differences force the requirements of a clock-gating insertion engine

Considering the restrictions that should apply for an automatic clock-gating insertion engine focused on *Latch* based designs and using the development environment provided by *Synopsys* as well as the code base existent in the synthesis tool developed by them, a prototype of clock-gating insertion for *Latches* is developed as part of *Design Compiler*<sup>®</sup>

The prototype embedded in *Design Compiler*<sup> $\mathbb{R}$ </sup> is tested against several small designs created for this purpose, and a larger design provided by a *Synopsys* customer and used in actual circuit development, which allows to test the tool robustness against large designs. RESUMEN DE LA MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA POR: JOAQUÍN RUBÉN JESÚS FIGUEROA ÁLVAREZ FECHA: JULIO 2012 PROF. GUÍA: VICTOR GRIMBLATT HINZPETER

#### CLOCK-GATING FOR LATCH BASED DESIGNS

Los circuitos digitales, que juegan un papel crucial en la vida cotidiana, consumen grandes cantidades de potencia lo que es considerado como una situación no deseada, lo que es particularmente cierto para equipos que dependen de baterías como celulares, es por esto que los diseñadores de circuitos así como las herramientas de síntesis utilizan diferentes técnicas con el fin de reducir su consumo de potencia.

Una de las técnicas de reducción de potencia mas exitosas es *clock-gating* cuyo objetivo es reducir el consumo de potencia generado por las transiciones debidas a la señal de **clk**. La reducción de potencia se logra mediante la inserción de *clock-gating cells*<sup>1</sup> que impiden que la señal de **clk** llegue a los *Flip-Flop* cuando el valor de la salida de estos no se espera que cambie.

Los diseños basados en *Latch*, que si bien no son tan utilizados como los diseños basados en *Flip-Flop* debido a sus complejidades adicionales, todavía son utilizados gracias a ciertos beneficios que presentan las restricciones de *timing*<sup>2</sup> de los *Latch*, sin embargo ninguna de las herramientas de síntesis existentes permite la inserción automática de *clock-gates* para diseños basados en *Latches*, por lo que los diseñadores de circuitos se ven forzados a insertar las *clock-gates* de forma manual lo que es ineficiente.

El presente trabajo se enfoca en los mecanismos de *clock-gating* y los requisitos que se deben cumplir para permitir su uso en diseños basados en *Latches* desde la perspectiva de una herramienta de síntesis, al tiempo que provee de una discusión teórica sobre las diferencias entre *Latches* y *Flip-Flops* y como estas diferencias fuerzan los requerimientos de una herramienta de inserción de *clock-gates*

Considerando las restricciones que debieran aplicar para una herramienta de inserción de *clock-gates* automática enfocada en *Latches* y utilizando el entorno de desarrollo provisto por *Synopsys* así como el código existente en la herramienta de síntesis desarrollada por ellos, se desarrolla un prototipo de inserción de *clock-gates* para *Latches* como parte de *Design Compiler*<sup>®</sup>

El prototipo una vez embebido en  $Design \ Compiler^{(\mathbb{R})}$  es probado en diversos diseños creados con este propósito y un diseño de mayor envergadura provisto por uno de los clientes de Synopsys y que es utilizado durante el desarrollo de circuitos reales, lo cual permite verificar la robustez de la herramienta desarrollada en diseños grandes.

<sup>&</sup>lt;sup>1</sup>celdas de clock-gating

<sup>&</sup>lt;sup>2</sup>timing o sincronización

A mi familia...

# Agradecimientos

A mi familia por su apoyo incondicional.

- A mi profesor guía por su ayuda.

- A los miembros de la comisión por ayudarme a mejorar la redacción.

A los ingenieros de *Synopsys* por ayudarme en los inicios de la investigación y en especial al grupo de clock-gating que me ayudo a comprender mejor el código para generar el prototipo adecuadamente.

# Contents

| 1        | Intr                  | roducti | on                                    | 1  |

|----------|-----------------------|---------|---------------------------------------|----|

|          | 1.1                   | Introd  | uction                                | 1  |

|          | 1.2                   | Object  | tives                                 | 2  |

|          |                       | 1.2.1   | General Objective                     | 2  |

|          |                       | 1.2.2   | Specific objectives                   | 2  |

|          | 1.3                   | Struct  | ure                                   | 2  |

| <b>2</b> | $\operatorname{Lite}$ | erature | Review                                | 4  |

|          | 2.1                   | Digita  | l circuits                            | 4  |

|          |                       | 2.1.1   | Digital circuit design advantages     | 6  |

|          |                       | 2.1.2   | Timing analysis on digital circuits   | 7  |

|          | 2.2                   | Seque   | ntial Circuits                        | 9  |

|          |                       | 2.2.1   | Finite State Machines                 | 10 |

|          |                       | 2.2.2   | Sequential Cells                      | 11 |

|          | 2.3                   | Synch   | ronous and Asynchronous Circuits      | 13 |

|          |                       | 2.3.1   | Synchronous Circuit advantages        | 14 |

|          | 2.4                   | Timin   | g parameters for timing analysis      | 15 |

|          |                       | 2.4.1   | Clock parameters                      | 15 |

|          |                       | 2.4.2   | Flip-Flop timing parameters           | 16 |

|          |                       | 2.4.3   | Latch timing parameters               | 16 |

|          | 2.5                   | Timin   | g equations of Latches and Flip-Flops | 17 |

|      | 2.5.1  | Flip-Flop set-up timing violation                             | 18 |

|------|--------|---------------------------------------------------------------|----|

|      | 2.5.2  | Flip-Flop hold timing violation                               | 20 |

|      | 2.5.3  | Latch set-up timing violation                                 | 22 |

|      | 2.5.4  | Latch hold timing violation                                   | 25 |

| 2.6  | Latch- | based Designs                                                 | 29 |

|      | 2.6.1  | Replacing <i>Flip-Flop</i> with <i>Latch</i>                  | 29 |

|      | 2.6.2  | Latch based design advantages                                 | 30 |

|      | 2.6.3  | Domino circuits                                               | 33 |

|      | 2.6.4  | Pulsed Latch                                                  | 36 |

| 2.7  | Power  | Consumption in CMOS circuits                                  | 37 |

|      | 2.7.1  | Dynamic power                                                 | 38 |

|      | 2.7.2  | Static Leakage Power                                          | 42 |

| 2.8  | Low-P  | ower design techniques for Integrated Circuits                | 43 |

|      | 2.8.1  | Supply Voltage Reduction                                      | 43 |

|      | 2.8.2  | Clock-gating                                                  | 44 |

|      | 2.8.3  | Multivoltage design                                           | 45 |

|      | 2.8.4  | Multiple-Vt library cells                                     | 46 |

|      | 2.8.5  | Power Switching                                               | 46 |

|      | 2.8.6  | Dynamic Voltage and frequency scaling                         | 47 |

| 2.9  | Clock- | gating for <i>Flip-Flop</i> based designs                     | 48 |

|      | 2.9.1  | Types of clock-gating cell                                    | 48 |

|      | 2.9.2  | Basic clock-gating insertion                                  | 51 |

| 2.10 | Advan  | ced clock-gating insertion for <i>Flip-Flop</i> based designs | 53 |

|      | 2.10.1 | Enhanced clock-gating insertion                               | 54 |

|      | 2.10.2 | Multistage clock-gating insertion                             | 56 |

|      | 2.10.3 | XOR Self-Gating                                               | 57 |

|      | 2.10.4 | Other clock-gating operations                                 | 59 |

| 2.11 Aproaches to clock-gating for <i>Latches</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | 60                                                                                                                                                         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 2.11.1 Pulser-gating                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       | 60                                                                                                                                                         |

| 3 Tool Development                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | 62                                                                                                                                                         |

| 3.1 Relevance of the work                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       | 62                                                                                                                                                         |

| 3.2 Auxiliar tools developed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                       | 62                                                                                                                                                         |

| 3.3 Timing analysis of a gated <i>Latch</i>                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                       | 63                                                                                                                                                         |

| 3.4 Analysis of the clock-gating insertion algorithm                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       | 65                                                                                                                                                         |

| 3.4.1 Design $Compiler^{\mathbb{R}}$ compile command flow                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                       | 65                                                                                                                                                         |

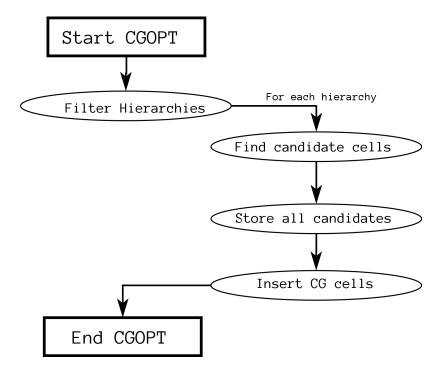

| 3.4.2 $CGOPT$ flow $\ldots$ $\ldots$ $\ldots$ $\ldots$ $\ldots$                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       | 67                                                                                                                                                         |

| 3.5 Clock-gating for <i>Latches</i> implementation                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | 68                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       | 68                                                                                                                                                         |

| 3.5.1 New Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       |                                                                                                                                                            |

| 3.5.1New Variables                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       | 69                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                       | 69<br>75                                                                                                                                                   |

| 3.5.2 Functionality modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       |                                                                                                                                                            |

| <ul><li>3.5.2 Functionality modifications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                       | 75                                                                                                                                                         |

| <ul> <li>3.5.2 Functionality modifications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       | 75<br><b>76</b>                                                                                                                                            |

| <ul> <li>3.5.2 Functionality modifications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       | 75<br><b>76</b><br>76                                                                                                                                      |

| <ul> <li>3.5.2 Functionality modifications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | · · · · · · · · · · · · · · · · · · · | 75<br><b>76</b><br>76<br>77                                                                                                                                |

| 3.5.2       Functionality modifications       .         3.6       Unit tests for the code       .         4       Analysis of Results         4.1       Unit test results       .         4.1.1       Mapped Latch clock-gating       .         4.1.2       Latch with feedback loop clock-gating       .                                                                                                                                                                                                              | · · · · · · · · · · · · · · · · · · · | 75<br><b>76</b><br>76<br>77<br>78                                                                                                                          |

| 3.5.2       Functionality modifications       .         3.6       Unit tests for the code       .         4       Analysis of Results         4.1       Unit test results       .         4.1.1       Mapped Latch clock-gating       .         4.1.2       Latch with feedback loop clock-gating       .         4.2       Customer testcase results       .                                                                                                                                                          |                                       | <ul> <li>75</li> <li>76</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> </ul>                                                                         |

| 3.5.2       Functionality modifications       .         3.6       Unit tests for the code       .         4       Analysis of Results       .         4.1       Unit test results       .         4.1.1       Mapped Latch clock-gating       .         4.1.2       Latch with feedback loop clock-gating       .         4.2       Customer testcase results       .         4.2.1       The testcase       .                                                                                                         |                                       | <ul> <li>75</li> <li>76</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> <li>79</li> </ul>                                                             |

| 3.5.2       Functionality modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                       | <ul> <li>75</li> <li>76</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> <li>79</li> <li>79</li> <li>79</li> </ul>                                     |

| 3.5.2 Functionality modifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                       | <ul> <li>75</li> <li>76</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> <li>79</li> <li>79</li> <li>79</li> <li>82</li> </ul>                         |

| <ul> <li>3.5.2 Functionality modifications</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                       | <ul> <li>75</li> <li>76</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> <li>79</li> <li>79</li> <li>82</li> <li>82</li> </ul>                         |

| 3.5.2       Functionality modifications          3.6       Unit tests for the code          4       Analysis of Results          4.1       Unit test results          4.1       Unit test results          4.1.1       Mapped Latch clock-gating          4.1.2       Latch with feedback loop clock-gating          4.2       Customer testcase results          4.2.1       The testcase          4.2.2       The results          5       Conclusions          5.1       Conclusions          5.2       Future Work |                                       | <ul> <li>75</li> <li>76</li> <li>76</li> <li>77</li> <li>78</li> <li>79</li> <li>79</li> <li>79</li> <li>79</li> <li>82</li> <li>82</li> <li>83</li> </ul> |

|   | 5    | 5.2.4 | Support some advanced features | 84 |

|---|------|-------|--------------------------------|----|

|   | E.   | 5.2.5 | $Formality^{(R)}$ support      | 84 |

| A | TCL  | Scrip | ots                            | a  |

| в | Unit | Tests |                                | d  |

# List of Figures

| 2.1  | Voltage level noise tolerance                                      | 5  |

|------|--------------------------------------------------------------------|----|

| 2.2  | Abstraction levels in digital design                               | 6  |

| 2.3  | Simple timing Diagram                                              | 7  |

| 2.4  | Static timing hazard                                               | 8  |

| 2.5  | Dynamic timing hazard                                              | 9  |

| 2.6  | Finite state machines                                              | 11 |

| 2.7  | S-R Latch                                                          | 12 |

| 2.8  | sequential elements                                                | 12 |

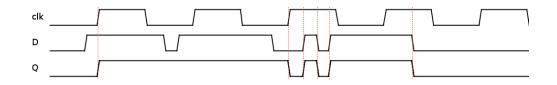

| 2.9  | Timing diagram of the <i>D Latch</i>                               | 13 |

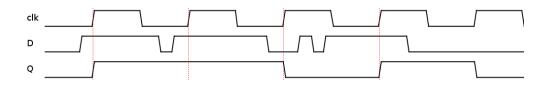

| 2.10 | Timing diagram of the <i>D</i> Flip-Flop                           | 13 |

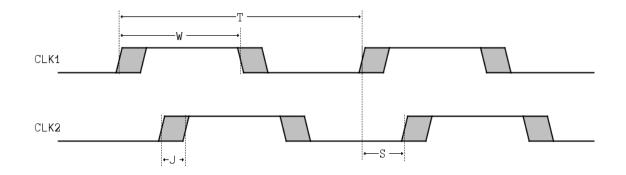

| 2.11 | Clock Parameters                                                   | 15 |

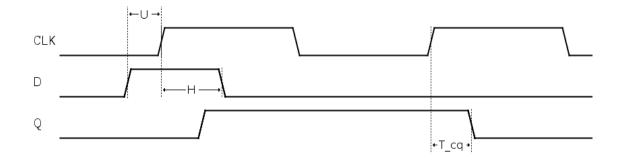

| 2.12 | Flip-Flop timing parameters                                        | 16 |

| 2.13 | Latch timing parameters                                            | 16 |

| 2.14 | Flip-Flop schematic for timing violations                          | 18 |

| 2.15 | Flip-Flop set-up timing restriction diagram                        | 18 |

| 2.16 | Flip-Flop schematic for hold timing violations analysis            | 20 |

| 2.17 | Timing diagram for <i>Flip-Flop</i> hold timing violation analysis | 20 |

| 2.18 | Latch schematic set-up                                             | 22 |

| 2.19 | Timing diagram for <i>Latch</i> set-up, late <b>clk</b>            | 22 |

| 2.20 | Timing diagram for <i>Latch</i> set-up, late data                  | 24 |

| 2.21 | Latch schematic hold                                               | 25 |

| 2.22 | Timing diagram for <i>Latch</i> hold, late data                        | 26 |

|------|------------------------------------------------------------------------|----|

| 2.23 | Timing diagram for <i>Latch</i> hold, late <b>clk</b>                  | 27 |

| 2.24 | Clock uncertainty absorption                                           | 30 |

| 2.25 | Static Time borrowing explanation                                      | 32 |

| 2.26 | Dynamic time borrowing explanation                                     | 33 |

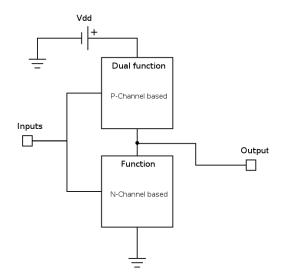

| 2.27 | Cmos basic design principle                                            | 34 |

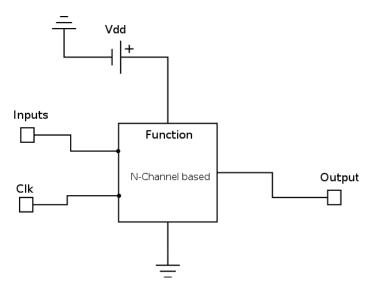

| 2.28 | Dynamic logic basic design principle                                   | 34 |

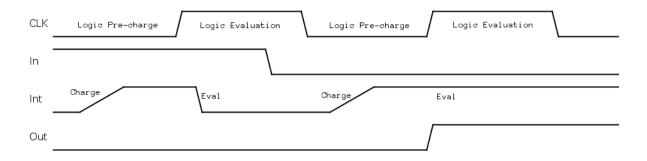

| 2.29 | Dynamic inverter timing diagram                                        | 35 |

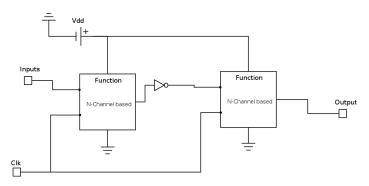

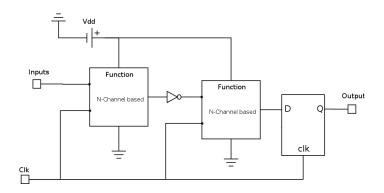

| 2.30 | Domino Logic design principle                                          | 35 |

| 2.31 | Domino logic with Latch                                                | 36 |

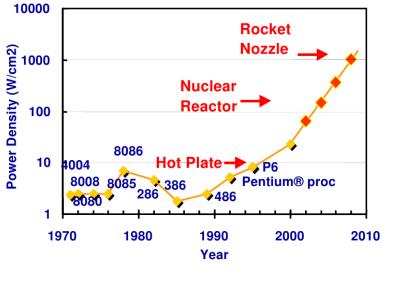

| 2.32 | Power density increase through time                                    | 38 |

| 2.33 | Rising edge transition currents                                        | 39 |

| 2.34 | Falling edge transition currents                                       | 39 |

| 2.35 | Crowbar-current during the transition                                  | 40 |

| 2.36 | Leakage currents flow                                                  | 42 |

| 2.37 | Basic clock-gating transformation                                      | 44 |

| 2.38 | A simple clock gate design                                             | 44 |

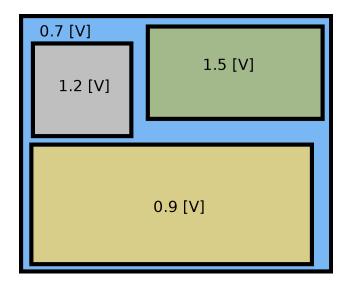

| 2.39 | Multivoltage design principle                                          | 45 |

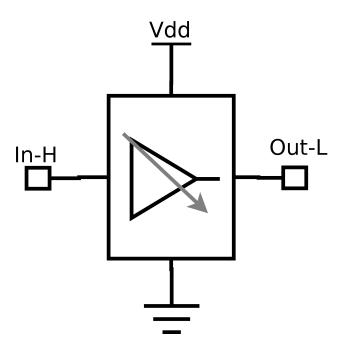

| 2.40 | Low to high level-shifter                                              | 46 |

| 2.41 | Power switching design principle                                       | 47 |

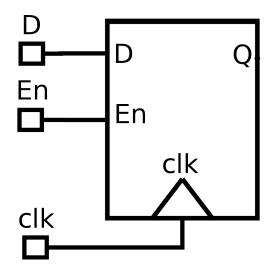

| 2.42 | Latch based positive edge triggered clock-gating cell                  | 48 |

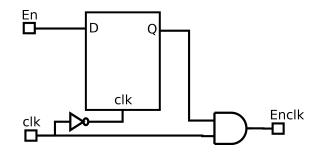

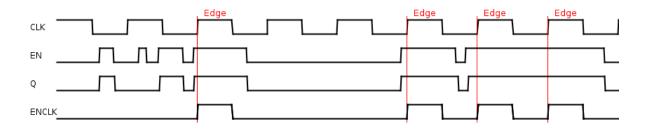

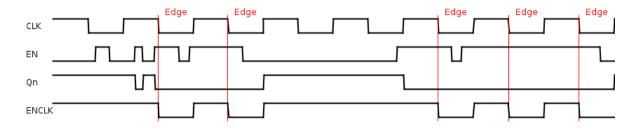

| 2.43 | Timing diagram for a latch based positive edge clock-gating cell       | 49 |

| 2.44 | Latch based negative edge triggered clock-gating cell                  | 49 |

| 2.45 | Timing diagram for a latch based negative edge clock-gating cell       | 49 |

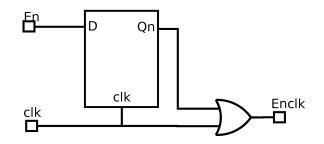

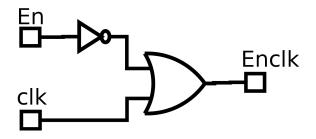

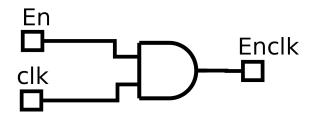

| 2.46 | Latch free positive edge triggered clock-gating cell                   | 50 |

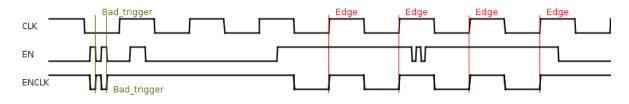

| 2.47 | Timing diagram for a <i>Latch</i> free positive edge clock-gating cell | 50 |

| 2.48 | latch free negative edge triggered clock-gating cell                   | 51 |

| 2.49 | Timing diagram for a latch free negative edge clock-gating cell                                                                                                                       | 51 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

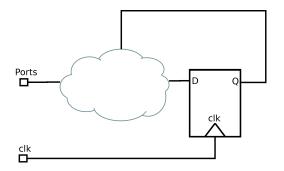

| 2.50 | <i>Flip-Flop</i> with enable pin                                                                                                                                                      | 52 |

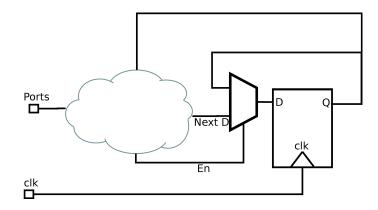

| 2.51 | Flip-Flop with feedback loop                                                                                                                                                          | 52 |

| 2.52 | <i>Flip-Flop</i> with feedback loop with a multiplexer representation                                                                                                                 | 53 |

| 2.53 | Flip-Flop with multiplexer and enable signal                                                                                                                                          | 53 |

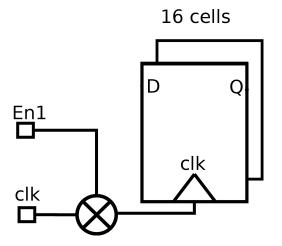

| 2.54 | Bank and a single register                                                                                                                                                            | 54 |

| 2.55 | Gated bank and a single register                                                                                                                                                      | 54 |

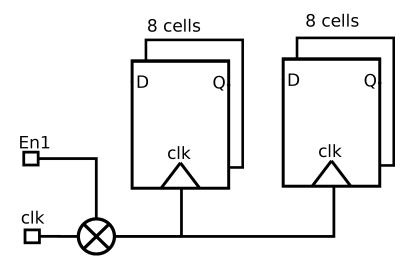

| 2.56 | Gated bank and register                                                                                                                                                               | 55 |

| 2.57 | Two single register                                                                                                                                                                   | 55 |

| 2.58 | Two gated registers                                                                                                                                                                   | 55 |

| 2.59 | Two banks of registers                                                                                                                                                                | 56 |

| 2.60 | Two banks of gated <i>Flip-Flop</i>                                                                                                                                                   | 56 |

| 2.61 | Two gated registers register                                                                                                                                                          | 57 |

| 2.62 | Single candidate register for XOR Self-gating                                                                                                                                         | 57 |

| 2.63 | Single register gated using XOR Self-gating                                                                                                                                           | 58 |

| 2.64 | Two registers gated using XOR Self-gating                                                                                                                                             | 58 |

| 2.65 | Large bank of gated registers                                                                                                                                                         | 59 |

| 2.66 | Balanced group of gated banks                                                                                                                                                         | 60 |

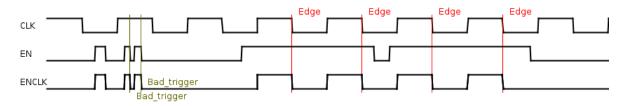

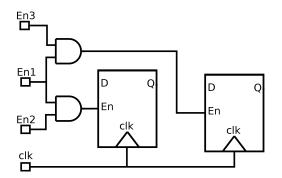

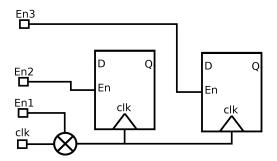

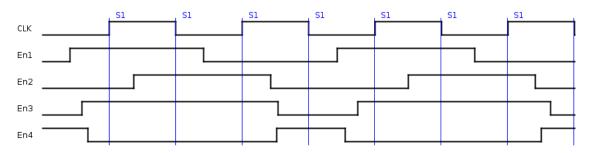

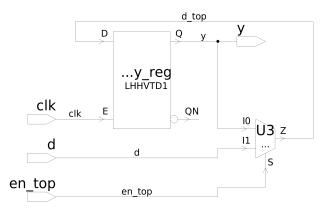

| 3.1  | Reasonable <b>EN</b> signals for <i>Latch</i> based designs                                                                                                                           | 64 |

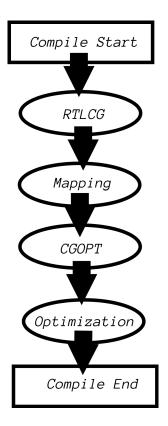

| 3.2  | Compile Flow                                                                                                                                                                          | 66 |

| 3.3  | Cgopt Flow                                                                                                                                                                            | 67 |

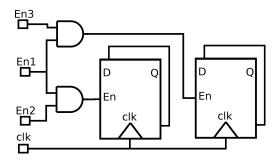

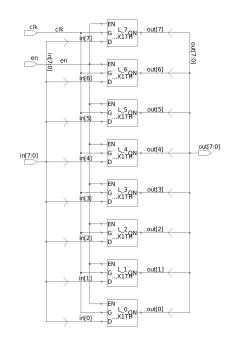

| 4.1  | Mapped Latches                                                                                                                                                                        | 77 |

| 4.2  | Gated bank of <i>Latches</i>                                                                                                                                                          | 77 |

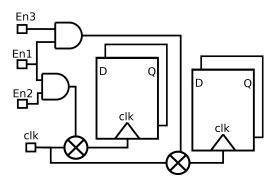

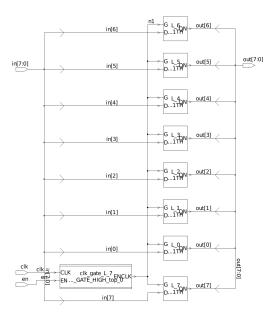

| 4.3  | Latch with feedback loop                                                                                                                                                              | 78 |

| 4.4  | Gated Latch using Design Compiler <sup>®</sup> $\ldots \ldots \ldots$ | 78 |

# List of Tables

| 4.1 | Comparison between the reference results and the clock-gating for <i>Latches</i> results in |    |

|-----|---------------------------------------------------------------------------------------------|----|

|     | the short flow                                                                              | 80 |

| 4.2 | Comparison between the reference results and the clock-gating for <i>Latches</i> results in |    |

|     | the full flow                                                                               | 80 |

# Chapter 1

# Introduction

### 1.1 Introduction

Digital circuits, a key element in modern life, embedded in almost any device nowadays, are built using CMOS transistors for their speed, small power consumption and constantly shrinking size. Usually those transistors are grouped in functional cells in order to take advantage of the higher abstraction level in circuit designs; among those designs sequential circuits are of special interest since they allow complex decision making and signal processing algorithms to be part of the circuit which allow the fastest processing by keeping computations in the hardware instead of using software. This allows the existence of  $ASIC^1$  and microprocessors.

Sequential circuit are built using sequential cells which are divided in two mayor families *Flip-Flops* and *Latches*. *Flip-Flops* are used in most circuit designs for their simpler timing properties allowing more robust designs with less effort, while *Latches* are used in less designs since requires more effort to ensure proper behavior, their less restraining timing characteristics allow faster designs<sup>2</sup>.

Unfortunately as complexity and requirements of digital circuits their power consumption rise accordingly thus most circuit designers have to make an additional effort in order to reduce power consumption of digital circuits. Most synthesis tools have embedded power reduction techniques. One of the most used power reduction techniques is clock-gating which currently is available only for *Flip-Flop* based designs

The present work studies the possibility of allowing automatic clock-gating insertion in *Latch* based designs using the *Synopsys* synthesis tool *Design Compiler*<sup>®</sup>; to do so this work provide information about *Flip-Flop* and *Latch* based designs, discussed the differences between the sequential elements and uses them to provide support for the clock-gating insertion for *Latches*.

$<sup>^1</sup>ASIC$  stands for Application specific integrated circuit

$<sup>^{2}</sup>$ Some *Latch* based designs are faster thanks to time-borrowing and usually *Latches* are used in other designs which are inherently faster, which is briefly discussed in chapter 2

Finally a prototype of clock-gating insertion for *Latches* is provided and the results of its application in different designs is discussed.

## 1.2 Objectives

The present work was defined with specific goals which are now introduced.

#### 1.2.1 General Objective

The general objective for this work is to provide a prototype of automatic clock-gating insertion for *Latch* based designs during the synthesis process of the circuit using the *Design Compiler*<sup>®</sup> software developed by *Synopsys*.

#### 1.2.2 Specific objectives

- Investigate tools and existent papers about the subject in order to insert clock-gates in *Latch* based designs

- Understand the differences between *Latches* and *Flip-Flops* in order to provide a correct solution for *Latch* based design clock-gating insertion

- Understand or develop theoretical support on the conditions for clock-gating insertion in *Latch* based designs

- Analyze possible problems that might arise in a clock-gating insertion for *Latches*

- Analyze possible clock-gating insertion mechanisms available for *Latch* based designs

- Develop a prototype of clock-gating insertion for *Latch* based designs

### 1.3 Structure

The present work is divided in several chapters that should be read in sequence in order to better understand it, as each chapter depends on the information provided by the former. Thus the following is a short description of the contents of each chapter.

Literature Review: The literature review chapter, provides insight in the theoretical fundamental and state of art of digital circuits and power reduction techniques. This chapter begins by providing a short introduction to the digital circuits theory to refresh some key concepts needed later, then the description of *Flip-Flop* and *Latch* based designs theory is visited as the understanding of the key differences between both sequential elements is crucial for the prototype development. The power reduction techniques are discussed next, they provide enough background on the power consumption of digital circuits and the different techniques used to reduce it, here is the clock-gating technique introduced, to later be explained in further detail showing the basic principle and why it's one of the most used techniques to reduce power consumption along with some advanced features available.

- **Tool Development:** This chapter realize the description of the steps to develop a prototype for clock-gating insertion for *Latch* based designs. The chapter starts by making a brief introduction to the current implementation in *Design Compiler*<sup>®</sup> for *Flip-Flop* clock-gating, this is performed by making a rough deception of the algorithm used to insert *CG* cells, and which parts of the code should be modified. Afterwards the description of the different auxiliary tools developed is made and finally some details on the modifications performed to the existent code are provided.

- **Analysis of results:** This chapter performs the analysis of the results of running the prototype tool in different designs, from small tests used for early verification to larger and more complex designs, analyzing the quality of the obtained results. Also performs a brief description of future work related to the tool and requirements for the prototype to enter to the *Production* status

- **Conclusions:** This is the final chapter of this work, provides the final round up for the different concepts treated here and summarizes the strengths and weakness of this feature.

# Chapter 2

# Literature Review

### 2.1 Digital circuits

Electronic circuits can be divided in 2 great families analog and digital circuits. The analog circuits are based on continuous quantities <sup>1</sup>; in this case these kind of circuits are based on voltage, and current so they can be interpreted intuitively by people, this way in a given circuit if the input voltage varies, then it's expected that the current must vary in a related way.

On the other hand, digital circuits are based on discrete quantities so they can't be interpreted with the same degree of intuition as analog circuits, because there is a threshold that must be surpassed in order to observe a difference in the behavior of the circuit given a change in the operating conditions of the circuit, in the same way a light's button must be pressed with a minimum force in order to turn-on or turn-off the light.

From a strict electric point of view there are more important difference between analog and digital circuits, as discussed by Roth on [1] and Floyd on [2]. Digital designs have several advantages over analog designs, being information compression, codification and reliability of the transferred information over a noisy channel, still analog circuits remain unbeaten in high fidelity audio systems where any compression would degrade the received audio quality.

The information compression is an immediate consequence of the quantification of the measured quantities and a sampling process, for example, in an analog temperature measurement scenario the temperature is fully measured continuously, while in a discrete scenario only fractions of the temperature are measured and at given intervals this way if the temperature were to be 35.342178 degrees, the analog circuit would measure the full temperature and a discrete would only measure the 35.3 degrees.

The codification in a digital system allows different ways of transmitting the data; in the temperature example the measured data could be transmitted as a voltage related proportionally

<sup>&</sup>lt;sup>1</sup> Common examples of continuous quantities are temperature or distance

to the measured temperature (which is called a discrete circuit) or codify the data in a different way, being one of the most common ways using a binary code transmitting a train of pulses directly related to the temperature.

When choosing a binary representation of the discrete data in a quantified circuit it's called a digital circuit, therefore in the following only binary data representation is used whenever a circuit is considered digital; in a digital circuit the following terms are used [3].

Logic level A voltage level that represents a defined digital state in an electronic circuit.

Logic HIGH (or Logic 1) The higher of two voltages in a digital system with two logic levels.

- Logic LOW (or Logic 0) The lower of two voltages in a digital system with two logic levels.

- **Positive logic** A system in which *Logic LOW* represents binary digit 0 and *Logic HIGH* represents binary digit 1.

- **Negative logic** A system in which *Logic LOW* represents binary digit 1 and *Logic HIGH* represents binary digit 0.

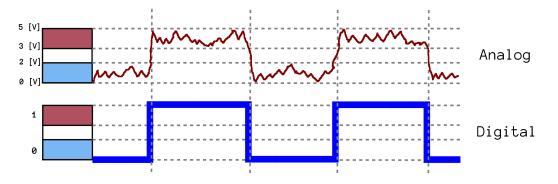

The reliability is a consequence of the data codification, by choosing a binary codification where a certain voltage represents the *Logic HIGH* and another the *Logic LOW*, there is a threshold where any signal above a threshold can be interpreted as *Logic HIGH* and any signal below another threshold represents the *Logic LOW* with no mistake implies high tolerance to noise during data transmission, as shown in the figure 2.1

Figure 2.1: The figure illustrates the reliability of a digital circuit. For a given circuit the *Logic* HIGH signal was defined as 5[V] with a threshold of 3[V], meaning that any voltage between 3[V] and 5[V] is recognized as a *Logic HIGH* signal; similarly the *Logic LOW* signal is defined as 0[V] with a threshold of 2[V] meaning that any voltage between 0[V] and 2[V] is recognized as *Logic LOW*. With these thresholds, the analog signal in the upper part of the figure is correctly recognized as the digital signal showed in the lower part of the image regardless of the associated noise in the analog transmission providing the robustness of the digital representation.

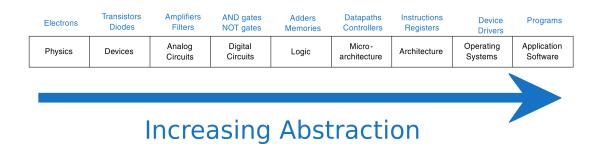

There is another advantage in digital circuits, also discussed in [4] is abstraction, which is the key for designing complex systems because all digital systems are built over analog circuits, yet digital circuits aren't designed transistor by transistor but over more complex units like logic gates<sup>2</sup>. The figure 2.2 [4]shows different levels of abstraction in a digital system design based on computer hardware and software.

Figure 2.2: This figure illustrates different abstraction levels in digital design [4]

#### 2.1.1 Digital circuit design advantages

From a design perspective, digital circuits have many advantages over analog circuits as discussed on [5]

- **Reproducible results:** For a given set of digital inputs, a digital circuit produces the same digital results every time, in contrast to analog circuits where there is no way to guarantee the same input<sup>3</sup>, and even if the exact same inputs are give, the result is not exactly the same because it's sensitive to different noise sources such as temperature

- **Programmable:** Digital circuits can be designed using a programmable approach using HDLs<sup>4</sup> therefore the circuits can be designed using a behavioral (or functional) description which is later translated to the corresponding netlist. Also the netlist can be simulated so the behavior of the circuit is verified prior actual implementation which is done automatically using special hardware and software, while analog circuit design doesn't have such features.

- **Flexibility and functionality:** Digital circuits can be designed to perform specific with high levels of complexity and perform such functions efficiently. Also the same circuit can perform different tasks depending on the inputs; this is the case of programmable circuits like micro-controllers and processors

$<sup>^{2}</sup>$  Logic gates are circuits built over transistors (typically) which operates on  $Logic \ levels$  like boolean functions (AND , OR )

<sup>&</sup>lt;sup>3</sup>Remember that in a analog circuit the input is sensitive to noise, while a digital circuit isn't as sensitive

<sup>&</sup>lt;sup>4</sup>HDL: Hardware description language

**Economy:** Digital circuits can be easily mass-produced in integrated circuits once the circuit has passed the prototype stage, making the mayor component of the circuit cost it's design time and prototyping. [6]

#### 2.1.2 Timing analysis on digital circuits

Logic cells and wires composing a digital circuit are far from ideal from the timing perspective because the time for a signal to traverse the circuit isn't 0, in fact every wire and logic gate in the signal path introduces finite delays to the data transmission, regardless of how small these delays can be, they should be taken into consideration in digital designs as they can affect the outputs [1]. Wire related delays are usually neglected, in comparison to the delays introduced by logic gates in timing analysis.  $^{5}$

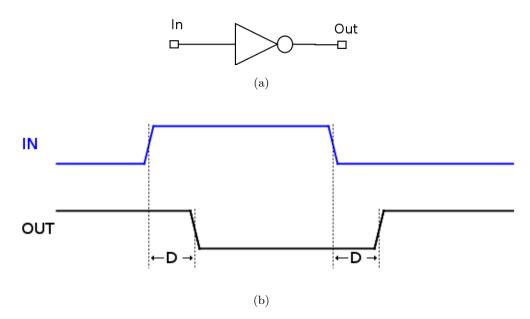

The best way to understand the timing of a simple design is using a timing diagram as the one shown in figure 2.3

Figure 2.3: (a) Shows the schematic of a simple inverter. (b) Shows the timing diagram of the inverter in (a) where the delay introduced by the inverter is shown as  $\mathbf{D}$

#### **Timing hazards**

Different timing delays through the datapath introduced by logic gates delays, causes dynamic behavior through the circuit when the input changes as the signal is propagated. This dynamic behavior may cause a difference between the expected result obtained by static analysis of the circuit and the observed output which behaves dynamically thus producing momentary differences

$<sup>^5\</sup>mathrm{Currently}$  as logic gates and transistors shrink, the delays of the logic gates becomes smaller closing the gap between both delays

between the expected result and the observer. This difference is known as *glitch* which corresponds to a quick transition between 2(or more) different outputs states when the static analysis predicted a different behavior. The timing hazards are divided in two categories [5].

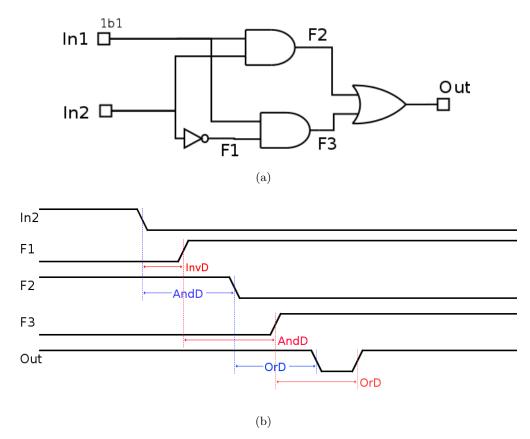

**Static Hazards:** A static hazard is a pair of input combination that differ only in one variable while both yield the same output signal, thus the output is expected to stay constant however the output changes momentarily before stabilizing to the expected result. An example of this is shown in figure 2.4

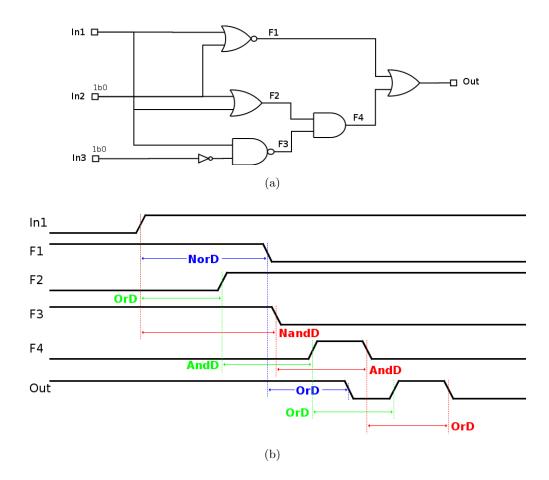

Figure 2.4: (a) Shows the schematic of a circuit susceptible to a static hazard. (b) Shows the timing diagram of the circuit shown in (a) where the signal In1 stays in Logic 1, while the signal In2 changes from Logic 0 to Logic 1, thus the timing diagram shows the signal propagation across the different logic stages in the circuit where the digital delays are illustrated as : **InvD** for the delay introduced by the inverter, **AndD** for the delays introduced by the AND gated and **OrD** for the delays introduced by the OR gates. The glitch is observed by the successive transitions in the output signal compared to the static analysis which predicted no transition in the output.

**Dynamic hazards:** A dynamic hazard a the result of multiple transitions in the output signal as result of a single input variable transition where the output was expected to change only once. An example of this is shown in the figure 2.5

Figure 2.5: (a) Shows the schematic of a circuit susceptible to a dynamic hazard. (b) Shows the timing diagram of the circuit shown in (a) for the transition of the input signal In1 from Logic 0 to Logic 1, while the signals In2 and In3 stay as Logic 0; the timing diagram illustrates the propagation of the signal across the logic to the output signal where the delays of the different logic gates are as follows: **NorD** is the delay of a NOR gate, **OrD** is the delay of a OR gate, **NandD** is the delay of a NAND gate and **AndD** is the delay of an AND gate. The glitch is observed by the successive transitions of the output signal while the static analysis predicts only the transition from Logic 1 to Logic 0

Designing hazard free circuits requires the designer to include redundant logic to the minimized design, as the inclusion of additional logic stabilizes the output signal for conflicting transitions. This can be achieved using a Karnaugh map or even including the full list of redundant functions, however this method is area expensive and such logic insertion should be avoided.

#### 2.2 Sequential Circuits

Digital circuits are divided in 2 categories: combinational and sequential circuits as discussed by Duek on [3] and Harris on [4].

- **Combinational circuits:** The main characteristic of combinational circuits it's that its output depends only of it's current input, therefore they are effective in direct operation such as real-time audio and video filtering and high-speed calculations.

- **Sequential circuits:** The output of a sequential circuit can't be analyzed by considering only its current input, because the output depends on all the previous sequence of inputs which gives them their name.

#### 2.2.1 Finite State Machines

Digital circuits are widespread used mainly because of sequential circuits for they allow decision making which enables the construction of finite states machines *Finite State Machine*; a *Finite State Machine* (as discussed in [7]) is a mathematical model composed of a finite number of states for representing the dynamic behavior of a complex system according to their sequence of inputs, where the definition of state is as follows. [5]

**State :** "The *state* of a sequential circuit is a collection of *state variables* whose values at any one time contain all the information about the past necessary to account for the circuit's future behavior"

There are two different kind of *Finite State Machine*, as discussed by Wakerly on [5] used for digital system modeling, the *Mealy* and *Moore Finite State Machine*.

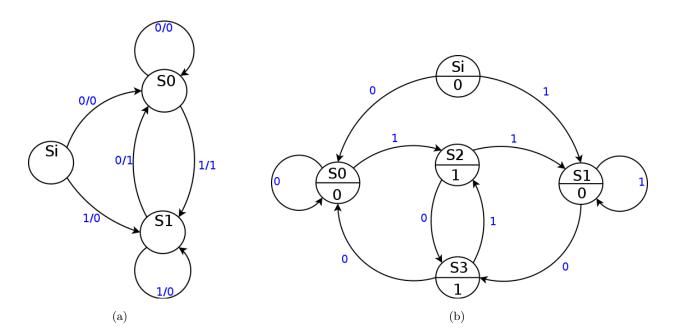

- *Mealy Finite State Machine* : The output of a *Mealy* machine like the one shown on figure 2.6(a) depends on the current state of the machine and it's current inputs.

- *Moore Finite State Machine*: The output of a *Moore* machine like the one shown on figure 2.6(b) depends only on the current state of the machine.

Figure 2.6: This figure shows the 2 mayor variants of *Finite State Machine* in digital system design. (a) Shows a basic *Mealy* machine. (b) Shows a basic *Moore* machine

Both types of *Finite State Machine* represent different approaches to solve the same problem, and both yield similar results, however a *Moore* machine is considered easier (and simpler) to implement in designs while a *Mealy* machine is usually considered more complex, but provides faster designs.

#### 2.2.2 Sequential Cells

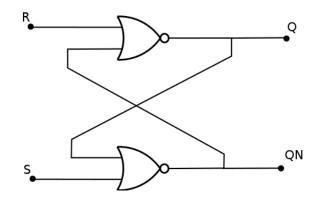

Sequential circuits are built using sequential elements and logic gates<sup>6</sup>; sequential elements are special cells with a bistable behavior, which, as discussed by Wakerly on [5], has two possible stable states and no other configuration is allowed, therefore if a bistable cell is in a given state, it can only go to the other state, there are no intermediate states allowed and as long as the cell is powered the cell won't change its state by noise. One of the most simple examples of a bistable cell is a *S*-*R* Latch shown in figure 2.7 [5]

<sup>&</sup>lt;sup>6</sup>Logic gates is the name given to circuits that perform boolean operations over it's circuits broken down to the basic operations (like AND,OR,NAND,NOR,NOT,XOR)

Figure 2.7: An S-R *Latch* as a collection of logic gates

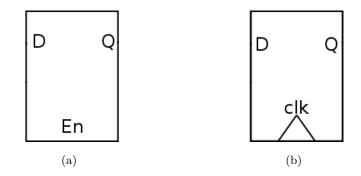

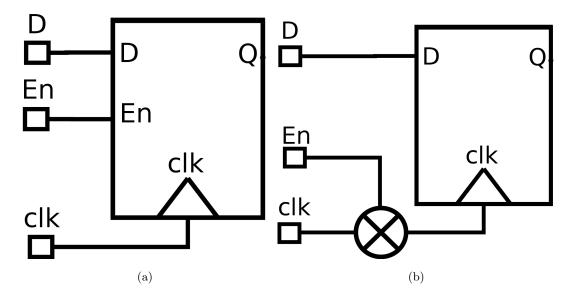

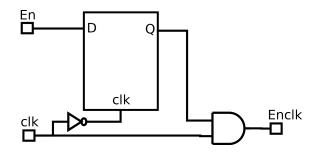

There are two families of bistables in digital circuit designs, *Latches* and *Flip-Flops*, being the output response to the change of data input the mayor difference between them. Even though there are several kind of *Latches* and *Flip-Flops*, only (*Positive logic*) *D Latches* and *D Flip-Flops* shown in Figure 2.8, are treated in this text, for they are the easiest to understand and model, therefore the most used variant of either *Latch* or *Flip-Flops* in digital circuits design.

Figure 2.8: This figure shows the most common representation of a D Latch and a D Flip-Flops (a) Shows the typical representation of a D Latch. (b) Shows the typical representation of a D Flip-Flop .

#### D Latch

The *D* Latch is a bi-stable element with 2 inputs ( usually named **D** and **EN** ) and typically 2 outputs (**Q** and **Q\_n**)<sup>7</sup>, the behavior of this component is dependent of the enable input (**EN** ) as whenever this signal corresponds to a Logic 1 the output's (**Q** ) value is exactly the same as the input's (**D** ) value, while the **Q\_n** output is always the logic inverse of the **Q** output. However as long as **EN** remains as a Logic 0 the outputs values won't change regardless of the input value. This behavior can be seen in the figure 2.9

<sup>&</sup>lt;sup>7</sup>In the present document, for simplicity, the **Q** output will be used while the **Q\_n** output is ignored unless necessary. Also some cells have only one of the outputs available from the *D* Latch cell in order to reduce the area of the cell; the same goes for a *D* Flip-Flop

Figure 2.9: Timing diagram of the *D Latch*. For for simplicity, the **EN** pin is fed with a **clk** signal

#### D Flip-Flop

The *D* Flip-Flop behavior is very similar to the *D* Latch, as both components have the same inputs and outputs, but the main difference between them is the response of the element against the control signal **EN**. The outputs only change in a Flip-Flop if the control signal experiments a transition between a Logic 0 and a Logic 1, keeping the stored value as long as there are no more transitions as seen on figure 2.10

Figure 2.10: Timing diagram of the D Flip-Flop . For for simplicity, the **EN** pin is fed with a **clk** signal

From now on, a D Latch will be referred unambiguously as Latch, while a D Flip-Flop will be named as Flip-Flop or just flop for simplicity.

In most applications the control signal used for the sequential elements is an externally generated periodic signal, a clock signal o  $\mathbf{clk}$ .

#### 2.3 Synchronous and Asynchronous Circuits

Sequential circuits can be further divide in synchronous and asynchronous circuits, depending on how the sequential cell are connected. Most circuits can be designed as a synchronous circuit and have a similar design performing the same task built as an asynchronous circuit. Each paradigm has advantages and disadvantages and the decision over which type of design use is based on in parameters like complexity, speed and robustness.

Asynchronous Circuits: Are circuits that are not controlled nor synchronized to an external clk signal, even if such signal exists, therefore are called asynchronous since there is no synchronization possible between the different state transitions of the circuit given the absence

of the control signal. These circuits if fed a **clk** signal use it only as reference and not as a control signal as the internal state-changes are controlled only by the logic and sequential cells delay.

**Synchronous Circuits:** Are circuits controlled by an external **clk** signal and the outputs of the circuit, along with all the internal state transitions, are synchronized with it, this is accomplished by connecting every sequential cell to the clock signal source, however this is not enough if the sequential cell is a *Latch* given the latch transparency window<sup>8</sup>

Asynchronous circuits might be considered faster than synchronous circuits, given that synchronous circuits depend on the clock signal for state transition, however synchronous circuits have several advantages over asynchronous circuits for they are simpler to design and more robust, since synchronous circuits can be analyzed using the same models as asynchronous circuits, yet the synchronizing **clk** signal simplifies the analysis while improving the design robustness, this has as result that basically all digital designs are synchronous, however asynchronous circuit analysis is still fundamental for analyzing interfaces between 2 different designs with different clock signal and still having a working circuit. [4]

#### 2.3.1 Synchronous Circuit advantages

Synchronous circuits are used because their timing analysis is simplified compared to the timing analysis of an asynchronous circuit, as the timing analysis is reduced to the analysis between the **clk** signal and the data signals, because the outputs and the internal states of the circuit are synchronized to the **clk** signal.

The timing analysis of a synchronous circuit is further simplified by using only Flip-Flops as sequential cells for their timing characteristics, previously discussed in 2.2.2, which allow the analysis to consider only a specific edge of the control signal, which in this case is the **clk**, and to compare it to the data arrival time, therefore as long as every the possible data signals arrive to the Flip-Flop before the **clk** signal for a given period the circuit will behave properly, therefore eliminating the need for analyzing the timing hazards of the circuits for most cases.

Since the timing analysis of a synchronous circuit is heavily simplified, circuits designers are able to focus on the functionality of the circuit, rather than preventing timing hazards, thus simplifying the design as the redundant logic needed to prevent the hazards is not necessary and leaving the timing analysis to a posterior stage. However timing analysis must not be overlooked as the maximum frequency of the circuit will be limited by the slowest logic path between 2 different sequential cells, therefore careless design negatively impacts the speed of the circuit.

$<sup>^{8}</sup>$ The transparency window is the time where the input signal of the *Latch* is propagated to the output. This will be discussed further in 2.4.3

#### 2.4 Timing parameters for timing analysis

In order to design an synchronous circuit, the synchronous behavior of the *Flip-Flop* regarding it's control signal makes it the easiest choice of sequential cell, however with careful design *Latches* can also be used as sequential cell and still obtain a *synchronous* behavior. Even if *Latches* don't have the synchronous behavior that *Flip-Flops* have, their smaller size, thus requiring less area and power than a *Flip-Flop* and better timing parameters, as discussed in [8] makes *Latches* an interesting alternative to *Flip-Flops* when designing high performance circuits.

The timing analysis of the *Flip-Flop* or *Latch* datapath requires the understanding of the timing parameters of the *Latch*, *Flip-Flop* and the clock parameters.

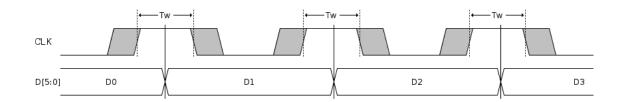

#### 2.4.1 Clock parameters

Figure 2.11: The clock parameters as discussed in [9], where T represents the period, W represents the duty cycle, J is the Jitter and S represents the clock-skew.

The clock signal used as reference in a synchronous design can be described using different parameters shown in figure 2.11, which are defined as following:

- Period: Is the time between 2 consecutive rising edge of the clk signal.

- **Duty cycle:** Is the time between the rising edge and the falling edge during a single period of the **clk** signal, also known as time window.

- **Jitter:** Is the local deviation in the period of the **clk** signal as noise for the same location, therefore is considered as random local noise since it's different on every period and different for each location in the circuit.

- **Clock skew:** Is time difference in the **clk** signal measured at 2 different locations of the circuit, therefore is considered a global noise and stable, since it depends on the circuit structure.

It becomes obvious that to describe an ideal **clk** signal is enough to define its period and duty cycle.

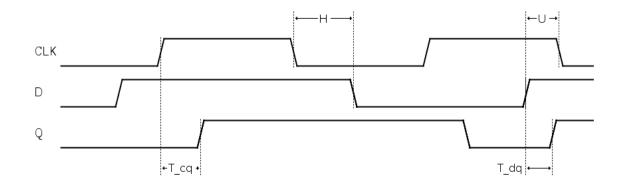

Figure 2.12: *Flip-Flop* timing parameters as discussed in [9], where U represents the set-up time, H represents the Hold time and  $T_{cq}$  represent the time clock-to-Q.

The *Flip-Flop* timing parameters as shown on figure 2.12 describe the behavior of the cell and its internal delays which are defined as following:

- **Set-up time:** Is the minimum time that the data signal must be stable before the end of the data capture in order to the signal to be handled properly. In the case of the *Flip-Flop* the end of the data capture corresponds to the rising edge of the **clk** signal.

- Hold time: Is the minimum time that the data signal must be stable after the end of the data capture of the cell in order to the signal to be handled properly. In the case of a *Flip-Flop* the end of the data capture corresponds to the rising edge of the clock signal.

- **Time clk-Q:** Or  $t_{cQ}$  is the internal delay of the *Flip-Flop* which indicates the time it takes for the input signal to be available at the output pin of the cell after the rising edge of the **clk** signal

#### 2.4.3 Latch timing parameters

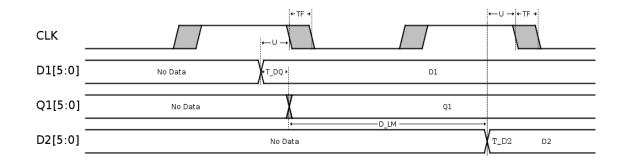

Figure 2.13: Latch timing parameters, as discussed in [9], where U represents the set-up time, H represents the Hold time,  $T_{cQ}$  represents the time clock-to-Q and  $T_{DQ}$  represents the time D-to-Q

The *Latch* timing parameters as shown on figure 2.13 describe the behavior of the cell and its internal delays regarding the control signal, which in this case is a **clk** for ease of comparison, which are defined as following:

- **Set-up time:** Just as defined in 2.4.2 represent the minimum time that the data input must be stable before the end of the capture time, which in a *Positive logic Latch* is the falling edge of the control signal.

- Hold time: Is the time that the data signal must be stable after the cell has stopped to capture data in order t handle it properly. The latch stops to capture data in the falling edge of the control signal.

- **Time clk-Q:** Is the time it takes to the data signal to be available at the output of the cell after a rising edge of the control signal (in this case the **clk**).

- **Time D-Q:** Is the time it takes to the input signal to be available at the output of the cell after a transition of the input signal while the control signal is in *Logic* 1, which means that the *Latch* is transparent.

From the timing parameters of the *Latch* and *Flip-Flop*, it becomes clear that as long as all data signals are timed in such a way that every transition of the data inputs of the sequential cell occurs only while the **clk** signal is in *Logic* 0, then there is no difference between a design where all the *Flip-Flop* cells are replaced with *Latches* as the *Latches* would behave as synchronously as *Flip-Flops* would. However this analysis is too simple and doesn't consider the timing differences between *Latches* and *Flip-Flops*.

### 2.5 Timing equations of Latches and Flip-Flops

The timing parameters of the *Latches* and *Flip-Flops* impose restrictions on the data arrival to a cell, therefore if the signal arrives after the set-up time of the cell, the cell is in a *Set-up timing Violation* and if the data input of a signal isn't stable during the Hold-time, then the cell is in a *Hold timing Violation*.

#### 2.5.1 *Flip-Flop* set-up timing violation

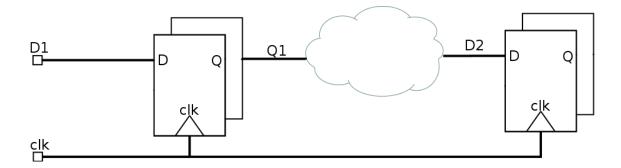

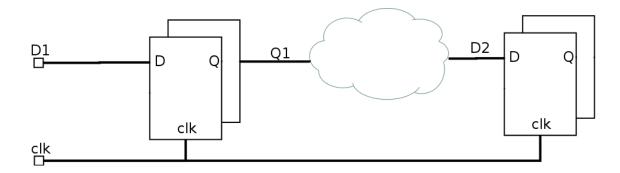

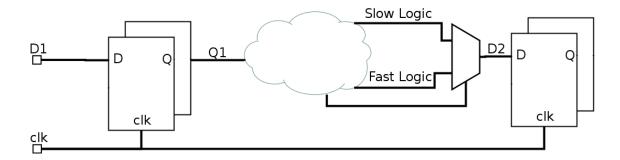

Figure 2.14: Flip-Flop schematic used as reference in the analysis of the set-up timing violations

(2.1)

$$T_{D_2} = R_1 + t_{DQ} + D_{L_M}$$

For the timing analysis of a Flip-Flop datapath, the circuit shown in figure 2.14 is used as reference, in the Set-up timing analysis, the data of the first Flip-Flop is assumed to have arrived at a proper time so the time it takes the signal to travel from the first Flip-Flop in the figure to the second is given for the equation 2.1 where :

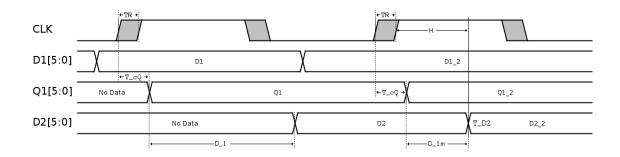

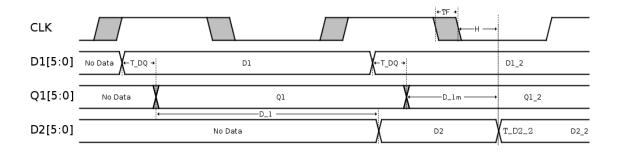

Figure 2.15: *Flip-Flop* timing diagram used as reference for the set-up timing violation analysis. This figure uses only one **clk** signal as reference for both *Flip-Flops* for simplicity, however in the analysis each bank is suposed to be fed with a slightly different **clk** signal derived from the same source.

- $T_{D_2}$  Is the time of arrival of the signal from the first *Flip-Flop* to the second *Flip-Flop* in the datapath

- $R_1$  Is the rising edge of the **clk** signal perceived by the first *Flip-Flop*

- $t_c Q$  Is the Time clk-Q of the first Flip-Flop

- $D_{{\cal L}_{\cal M}}$  Is the maximum logic delay from the output of the first  ${\it Flip}{\it -Flop}$  to the second  ${\it Flip}{\it -Flop}$  .

And figure 2.15 is used to illustrate the scenario described.

$$(2.2) T_{D_2} \le R_2 - U$$

The data arrival to the second Flip-Flop must comply the set-up condition, shown in equation 2.2, where:

$R_2$ : Is the rising edge in the **clk** pin of the second *Flip-Flop*.

U: Is the set-up time of the second *Flip-Flop*

Therefore the timing restriction is obtained by using equations 2.1 and 2.2 obtaining the equation 2.3.

$$(2.3) R_1 + t_{cQ} + D_{L_M} \le R_2 - U$$

The equation 2.3 is not complete as the information of the rising edges, which are defined by equations 2.4 and 2.5 where the value of "n" is assigned to match the corresponding edge, is not yet included in the equation.

$$(2.4) R_1 = n \cdot T + t_r$$

$$(2.5) R_2 = n \cdot T + t_r$$

By following a conservative approach for the rising edges defined by previous equations where T is the period of the signal and  $t_r$  is the uncertainty of the rising edge, equations 2.4 and 2.5 become 2.6 and 2.7 respectively, where  $T_R$  is the worst rising edge uncertainty.

$$(2.6) R_1 = n \cdot T + T_R$$

(2.7)

$$R_2 = (n+1) \cdot T - T_R$$

Finally by using the equations 2.6 and 2.7 on the equation 2.3 with simple algebraic manipulation becomes the equation 2.8 which is the timing restriction of the *Flip-Flop* and the period given by the set-up time.

$$(2.8) T \ge t_{cQ} + D_{L_M} + U + 2T_R$$

#### 2.5.2 *Flip-Flop* hold timing violation

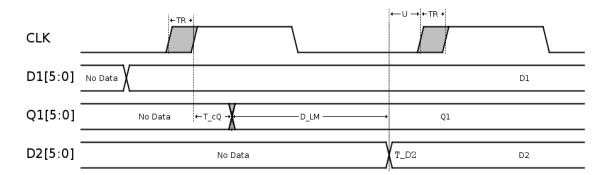

Figure 2.16: *Flip-Flop* schematic used as reference for the hold timing violations analysis. Shows a explicit difference between a slow (or regular) datapath and a faster datapath.

Figure 2.17: Timing diagram for the *Flip-Flops* used as reference for the hold-timing violation analysis. This figure uses only one **clk** signal as reference for both *Flip-Flops* for simplicity, however in the analysis each bank is suposed to be fed with a slightly different **clk** signal derived from the same source.

For the *Flip-Flop* hold timing violation analysis, the figure 2.16 is used as reference to better illustrate the circuits condition, also the figure 2.17 is used to illustrate the timing conditions analyzed.

(2.9)

$$T_{D_{2-2}} = R_1 + T_{cQ} + D_{l_m}$$

From figure 2.17 the arrival of the problematic signal  $T_{D_{2-2}}$  is given by the equation 2.9 where:

$R_1$ : Is the rising edge in the first *Flip-Flop*

$D_{l_m}$ : Is the minimum logic delay given by the datapath between the first and second *Flip-Flop*  $t_{cQ}$ : Is the *Time clk-Q* of the first *Flip-Flop*

$$(2.10) T_{D_{2-2}} \ge R_2 + H$$

However for the signal to comply the hold restriction, the time of arrival of the signal must follow the restriction set by the equation 2.10 where:

$F_2$ : Is the rising edge of the **clk** signal received by the second *Flip-Flop*.

H: Is the hold time of the second Flip-Flop

$$(2.11) R_1 + T_{cQ} + D_{l_m} \ge R_2 + H$$

From equations 2.9 and 2.10 the hold timing restriction for a Flip-Flop is given by the equation 2.11, where the rising and falling edge are given by the equation 2.4 and 2.5 respectively.

$$(2.12) R_1 = n \cdot T - T_R$$

$$(2.13) R_2 = n \cdot T + T_R$$

By considering the worst case scenario for the **clk** signals arriving each *Flip-Flop*, the rising edge of the cells are given by the equations 2.12 for the rising edge of the first cell where the clock arrived the earliest possible time and the equation 2.13 for the rising edge of the second cell where the **clk** signal arrived at the latest possible time. Finally by combining equations 2.11, 2.12 and 2.13; using simple algebraic manipulation the restriction over the fastest logic in the design based on the hold timing requirement of a *Flip-Flop* cell is represented by the equation 2.14.

$$(2.14) D_{l_m} \ge 2T_R + H - t_{cQ}$$

#### 2.5.3 Latch set-up timing violation

Figure 2.18: Latch schematic used as reference in the analysis for the set-up timing violations

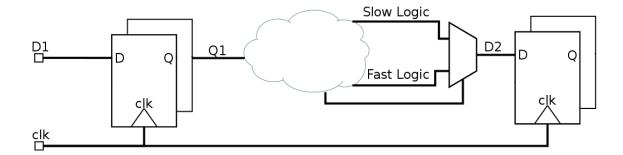

Figure 2.18 shows the schematic of a circuit composed of 2 banks of latches which is used as reference for the timing analysis of the set-up condition. Given the *Latches* timing characteristics, there are 2 possible scenarios for a set-up timing restriction.

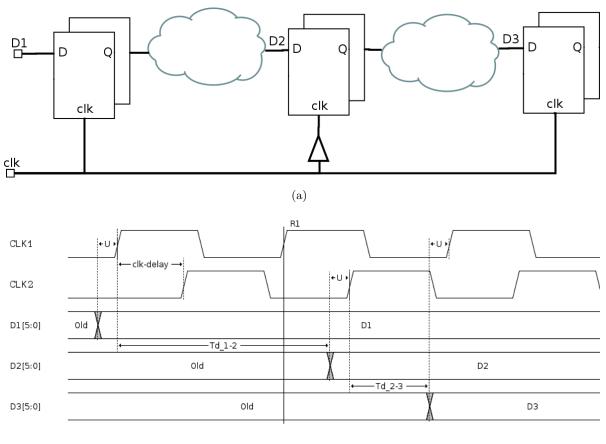

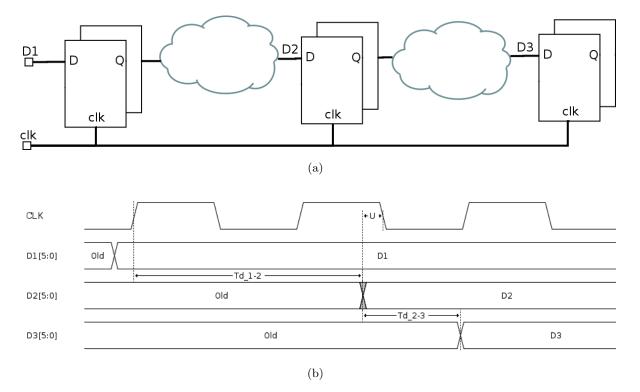

#### Latch set-up timing: late clk signal

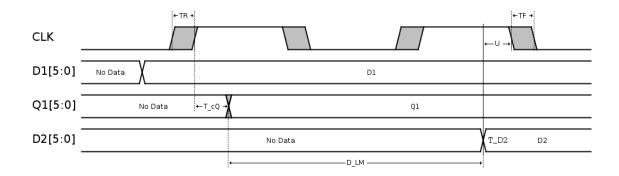

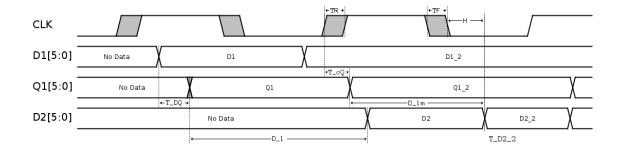

Figure 2.19: Timing diagram for the *Latches* used as reference for the set-up timing violation analysis, in the case when the data in the first *Latch* arrives before the **clk** signal which arrives at the latest possible time. This figure uses only one **clk** signal, for simplicity, as reference for both *Latches*, however in the analysis each bank is suposed to be fed with a slightly different **clk** signal derived from the same source.

(2.15)

$$T_{D_2} = R_1 + t_{cQ} + D_{L_M}$$

When the data of the first *Latch* arrives before the **clk** signal, as shown in the figure 2.19 the data arrival to the second latch is given by the equation 2.15 where:

$R_1$ : Is the rising edge of the first *Latch*

$t_{cQ}$ : Is the *Time clk-Q* of the first *Latch*

$D_{L_M}$ : Is the maximum logic delay of the circuit.

$$(2.16) T_{D_2} \ge F_2 - U$$

However the set-up requirement given by the equation 2.16, where:

$F_2$ : Is the falling edge of the **clk** signal in the second *Latch*

$U{:}$  Is the set-up time requirement of the Latch

$$(2.17) R_1 + t_{cQ} + D_{L_M} \le F_2 - U$$

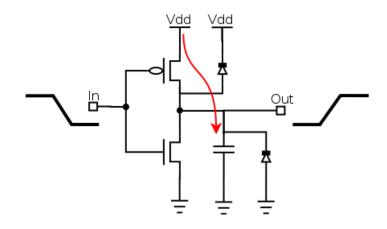

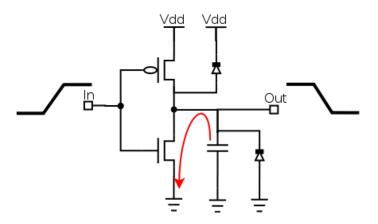

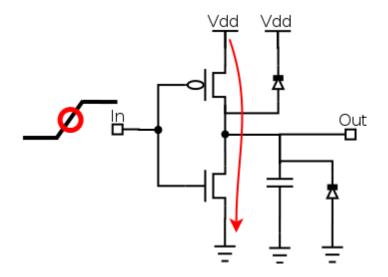

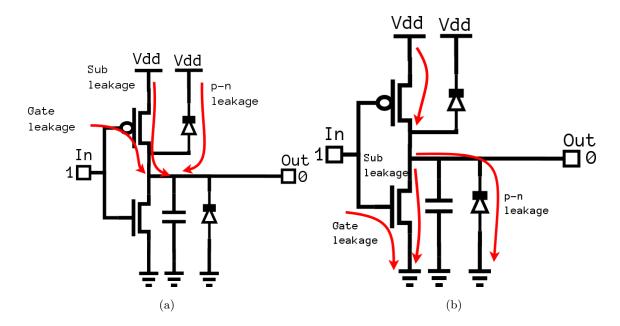

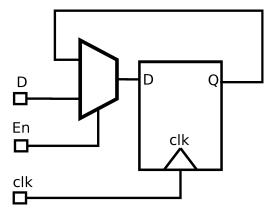

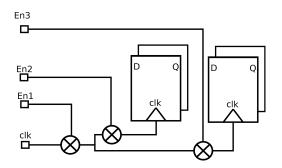

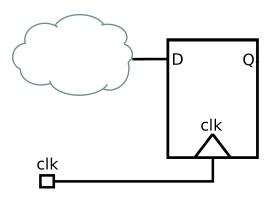

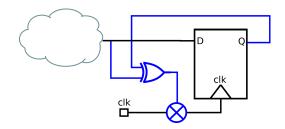

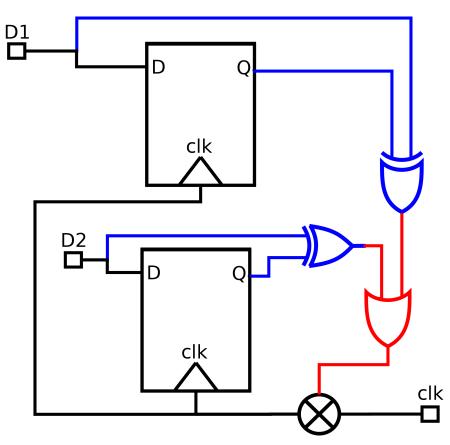

$$(2.18) F_2 = n \cdot T + W + t_f$$