# DISEÑO E IMPLEMENTACIÓN DE UN SISTEMA DE ACCIONAMIENTO Y RECEPCIÓN DE SEÑALES ULTRASÓNICAS PARA UN ECÓGRAFO ULTRA-PORTATIL

#### MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA

#### MANUEL ENRIQUE TOLEDO CHAMORRO

PROFESOR GUÍA: SR. NICOLÁS BELTRÁN MATURANA

MIEMBROS DE LA COMISIÓN: SR. HECTOR AGUSTO ALEGRÍA SR. MANUEL DUARTE MERMOUD

> SANTIAGO DE CHILE ABRIL 2012

RESUMEN DE LA MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA POR: MANUEL TOLEDO CHAMORRO FECHA: 25 DE ABRIL DE 2012

PROF.GUÍA: SR. NICOLÁS BELTRÁN MATURANA

#### "DISEÑO E IMPLEMENTACIÓN DE UN SISTEMA DE ACCIONAMIENTO Y RECEPCIÓN DE SEÑALES ULTRASÓNICAS PARA UN ECÓGRAFO ULTRA-PORTATIL"

Hoy en día es imposible imaginar no contar con la disponibilidad de acceso a exámenes médicos, que permitan la visualización de órganos y tejidos mediante sistemas no invasivos y de fácil aplicación, como son los ecógrafos. Sin embargo, en el presente se buscan más aplicaciones a este versátil método de examinación, como lo es la construcción de dispositivos ultra-portátiles, que permitan la ejecución de exámenes rutinarios de imagenología, pero en espacios reducidos y con un equipo energizado por baterías. Estadísticamente, es sabido que del total de las ecografías solicitadas; solo el 30% son realmente necesarias, por lo tanto, la inclusión de equipos de rápido acceso y de categoría portable, es un eslabón deseable en el proceso de diagnóstico médico. Es por ello que en esta memoria se plantea el diseño y fabricación de una plataforma electrónica que permita el manejo completo de un transductor ultrasónico, para realizar la construcción de este tipo de dispositivos.

En este documento se describen los fundamentos, procedimientos y resultados obtenidos en la implementación de un sistema de accionamiento y recepción de señales, para la generación de imágenes de ultrasonido. En esta dirección, se presentan diseños, simulaciones, implementaciones y la construcción de diversas plataformas que otorgaron el aprendizaje necesario para la confección de un sistema de alta tecnología con condiciones de estado del arte en pulsación ultrasónica. Estas iteraciones, son directa consecuencia de una búsqueda estricta de optimizaciones para la plataforma definitiva. Adicionalmente, se presenta todo el desarrollo y análisis necesario para lograr la puesta en marcha de un transductor ultrasónico activo con multiplexión local. Esto, con el fin de poder utilizar un dispositivo de bajo costo "after markel", en contraposición a la expectativa de fabricar un transductor ultrasónico personalizado con altos costos de inversión y construcción, asociado a la baja cantidad de unidades a producir en relación al mercado mundial abastecido por China. Finalmente, se expone la generación de una completa plataforma digital basada, que permite capturar los datos salientes de un sistema de conversión análogo/digital con interfaz serializada, grabar temporalmente en una memoria de acceso aleatorio de alta velocidad, y finalmente volcar datos a un servidor donde se realizará la conformación.

Tanto los desarrollos electrónicos como los de software, fueron íntegramente diseñados partiendo desde cero, contando únicamente con los conocimientos recabados durante una larga etapa de investigación. El diseño, cálculo y simulaciones de las plataformas, la confección de los circuitos impresos y el montaje de los componentes fue realizado en los laboratorios del Departamento de Ingeniería Eléctrica de la Universidad de Chile, en el contexto del proyecto Corfo Innova 09IEI-7183.

Los resultados obtenidos permiten concluir que se completó de forma íntegra la cadena de diseño, partiendo desde el estudio de la tecnología actual, llegando a la construcción de un dispositivo que se puede considerar estado del arte en el ámbito de pulsación de piezoeléctricos para equipos de ultrasonografía. Se logró obtener una plataforma funcional, eficiente y con gran robustez a los ciclos de trabajo estrictos a los que fue sometido.

"...Sé tu mismo. Especialmente no finjas afectos. Tampoco seas cínico respecto al amor, porque frente a toda aridez y desencanto, el amor es tan perenne como la hierba. Acepta con cariño el consejo de los años, renunciando con elegancia a las cosas de juventud. Nutre la fuerza de tu espíritu para que te proteja en la inesperada desgracia, pero no te angusties con fantasías. Muchos temores nacen de la fatiga y la soledad. Más allá de una sana disciplina, sé amable contigo mismo. Eres una criatura del universo, al igual que los árboles y las estrellas; tienes derecho a estar aquí. Y, te resulte o no evidente, sin duda el universo se desenvuelve como debe. Por lo tanto, mantente en paz con Dios, de cualquier modo que le concibas, y cualesquiera sean tus trabajos y aspiraciones. Mantente en paz con tu alma en la ruidosa confusión de la vida."

Desiderata, Max Ehrmann.

# Agradecimientos

Este documento es el ícono que cierra un proceso de largos 18 años de estudio, en los cuales busqué hambriento las herramientas para poder darle al mundo mi pasión, mi arte.

El camino recorrido hasta aquí está entregando un gran fruto y trascenderá como un granito de conocimiento más entregado a la humanidad, sin embargo este gran fruto del que me siento orgulloso no habría sido posible sin la existencia del motor de mi pasión: mi gente. Por eso he decidido dedicar estas líneas a quienes también les pertenece este trabajo.

Antes que a nadie, quiero agradecer a Dios, pues es la razón de hacer, la razón de creer, la razón de sentir y la razón de amar.

A mis padres, mi padre Manuel Toledo por su sabiduría y amor, por la disciplina que inculcó, y que siempre llevaré en mi corazón; a mi madre Verónica Chamorro, por su preocupación y su afecto, por entregarlo todo sin medida, por entregarme amor en cada segundo de su vida. Por el esfuerzo y el cariño que ambos depositaron siempre en mi, muchas gracias.

A mi hermano Patricio Toledo, mi favorito y mi elegido, un luchador del cual me siento inmensamente orgulloso y que cada día admiro más. Recuerda que siempre estaré contigo.

A mi amada, Rocío Clavijo, mi compañera de vida, la inspiración, motivación y razón de mis sueños; su amor, comprensión y respeto son mi tesoro más preciado, y el motor de mis ideales.

A mi madrina Nina, María Yolanda Chamorro por su afecto y por sus constantes plegarias para que Dios me acompañara.

A mis buenos amigos, Eduardo Ubilla, Claudio Tapia, Matías Cerda y Benjamín Olivares por su cariño y preocupación hacia mí y hacia mi familia.

A mis guías y compañeros en este fantástico proyecto: Profesor Nicolás Beltrán, Profesor Manuel Duarte, Rodrigo Maureira, Vader Johnson y Javier Moya.

Y por supuesto al Profesor Marcos Orchard, un verdadero ícono en mi vida universitaria que recordaré por siempre.

# Índice Generales

| Agradecimientos                                                                              | 4          |

|----------------------------------------------------------------------------------------------|------------|

| Índice Generales                                                                             | 5          |

| Índice de Figuras                                                                            | 7          |

| Capítulo 1 Introducción                                                                      | 9          |

| 1.1 Motivación                                                                               | 9          |

| 1.2 Hipótesis de trabajo y metodología                                                       | 10         |

| 1.3 Objetivos generales                                                                      | 10         |

| 1.4 Objetivos específicos                                                                    | 10         |

| 1.5 Estructura de la memoria                                                                 | 11         |

| Capítulo 2 Fundamentos Generales                                                             | 12         |

| 2.1 Funcionamiento básico de un equipo de ultrasonido                                        | 12         |

| 2.2 Transductores ultrasónicos                                                               | 15         |

| 2.2.1 Piezoeléctricos                                                                        |            |

| 2.2.2 Contextualización de los piezoeléctricos en el proyecto                                | 17         |

| 2.3 Multiplexión                                                                             | 18         |

| 2.3.1 Contextualización de la multiplexión en el proyecto                                    | 19         |

| 2.4 Pulsación                                                                                |            |

| 2.4.1 Transistores MOSFET para conmutación                                                   |            |

| 2.4.2 Estado del arte de los sistemas de pulsación                                           | 21         |

| 2.4.3 Contextualización de la pulsación en el proyecto                                       |            |

| 2.5 Conector                                                                                 |            |

| 2.6 Etapa de adquisición de señales                                                          |            |

| 2.6.1 FPGA                                                                                   |            |

| 2.6.2 Pares diferenciales LVDS                                                               |            |

| 2.7 Etapa de procesamiento de señales                                                        |            |

| 2.8 Dominio y aporte del trabajo                                                             |            |

| Capítulo 3 Diseño e implementación de sistemas                                               |            |

| 3.1 Diseño e implementación de sistema de pulsación Pulser v.1.0                             | 31         |

| 3.1.1 Drivers de corriente para MOSFETs                                                      |            |

| 3.1.2 Translación de referencias y pulsadores                                                |            |

| 3.1.3 Confección de PCBs                                                                     |            |

| 3.2 Análisis y puesta en marcha del sistema de multiplexión                                  | 36         |

| 3.2.1 Situación inicial del sistema de multiplexión                                          | 36         |

| 3.2.2 Diseño e implementación del sistema de control para la multiplexión                    |            |

| 3.3 Diseño e implementación del sistema de pulsación Pulser v.2.0                            |            |

| 3.3.1 Reemplazo de transistores MOSFET                                                       |            |

| 3.3.2 Confección de PCB                                                                      |            |

| 3.4 Migración de sistemas de control a FPGA                                                  |            |

| 3.4.1 Operación quasi-asíncrona del sistema de pulsación.                                    |            |

| 3.5 Diseño e implementación del sistema de pulsación Pulser v.2.5                            |            |

| 3.5.1 Simulación e inclusión del sistema de clamping                                         |            |

| Capítulo 4 Resultados, fabricación y pruebas de nuevas versiones, y desarrollos en recepción |            |

| 4.1 Resultados de implementación para el Pulser v.2.5                                        |            |

| 4.2 Diseño de sistema de pulsación Pulser v.3.0                                              |            |

| 4.2.1 Circuito integrado de pulsación                                                        |            |

| 4.2.2 Confección de PCB para Pulser v.3.0                                                    |            |

| 4.2.3 Resultados de operación para el Pulser v.3.0                                           | <b>3</b> 9 |

| 4.3 Desarrollo de núcleos para recepción digital                                  | 61             |

|-----------------------------------------------------------------------------------|----------------|

| 4.3.1 SERDES LVDS                                                                 | 63             |

| 4.3.2 SRAM                                                                        | 63             |

| 4.3.3 RS232                                                                       | 64             |

| 4.3.4 Implementación del esquema final completo                                   | 65             |

| Capítulo 5 Conclusiones Generales y Trabajo Futuro                                | 67             |

| 5.1 Conclusiones Generales                                                        | 67             |

| 5.2 Trabajo Futuro                                                                | 68             |

| Referencias                                                                       | 70             |

| Anexos                                                                            | 73             |

| Anexo 1: Diagramas de sistema de pulsación "Pulser v.1.0"                         | 73             |

| Anexo 2: Código C para 16F877A decodificador de multiplexión                      | 75             |

| Anexo 3: Esquema funcional de plataforma de control para multiplexión y pulsación | n76            |

| Anexo 4: Módulo de comandos abstractos de multiplexión y pulsación                | 77             |

| Anexo 5: Módulo de interrelación y coherencia de datos                            | 78             |

| Anexo 6: Módulo de interpretación de direccionamiento                             | 78             |

| Anexo 7: Módulo de comunicación con los multiplexores                             | 85             |

| Anexo 8: Módulo Verilog de pulsación asíncrona                                    | 90             |

| Anexo 9: Núcleo para utilización y pruebas del módulo de manejo para SRAM         | 92             |

| Anexo 10: Núcleo para utilización del módulo de transmisiones RS232               |                |

| Anexo 11: Código de software de recepción para el host en Visual Basic            | 101            |

| Anexo 12: Códigos de módulos y núcleos para el funcionamiento del sistema         | de adquisición |

| completo.                                                                         | 104            |

|                                                                                   |                |

# Índice de Figuras

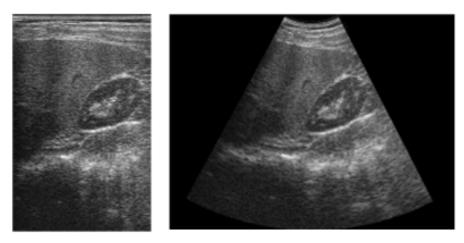

| Figura 1: (Izquierda) Imagen original, (Derecha) Imagen procesada a través de un Scan Convei | ter 14 |

|----------------------------------------------------------------------------------------------|--------|

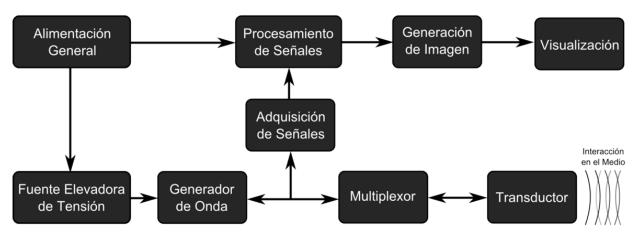

| Figura 2: Diagrama de bloques general de operación de un ecógrafo ultra-portatil             | 15     |

| Figura 3: Transductor lineal de 4 cm. de excursión.                                          | 15     |

| Figura 4: Transductor ultrasónico de 80 elementos, con conector convencional                 |        |

| Figura 5: Trozo de cerámica perovskita en bruto.                                             |        |

| Figura 6: Fotografía del cabezal piezoeléctrico utilizado.                                   | 17     |

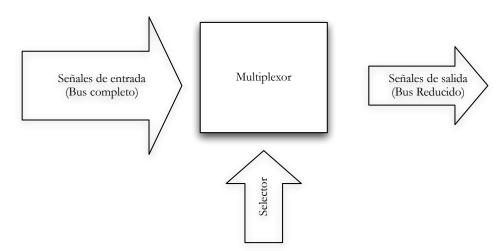

| Figura 7: Esquema básico de funcionamiento de un multiplexor.                                | 18     |

| Figura 8: Fotografías de la situación interna del transductor ultrasónico                    |        |

| Figura 9: Modelo Físico Electrónico de un transistor MOSFET.                                 | 20     |

| Figura 10: Circuito clásico de configuración push-pull.                                      |        |

| Figura 11: Esquema de pulsación unipolar clásico usado                                       |        |

| Figura 12: Arquitectura electrónica de un pulser bipolar.                                    | 23     |

| Figura 13: Topología de pulsación con clamper                                                |        |

| Figura 14: Arquitectura de pulsación propuesta en las notas de aplicación de Supertex® Inc   | 25     |

| Figura 15: Arquitectura Propuesta por National Semiconductor ®.                              |        |

| Figura 16: Comparativa de tamaños para los conectores de transductores.                      |        |

| Figura 17: Encapsulado FPGA que se usará para los desarrollos.                               |        |

| Figura 18: Esquema de funcionamiento para un sistema de transmisión LVDS                     |        |

| Figura 19: Configuración de salidas paralelas para obtención de mayor Fan-Out                |        |

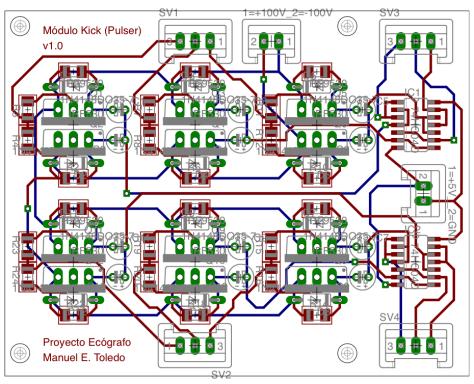

| Figura 20: Esquemático del circuito para un pulsador (Versión 1.0)                           |        |

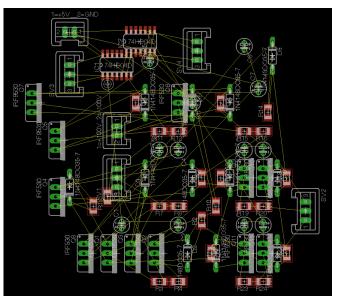

| Figura 21: Modelo de la PCB para construcción del Pulser v1.0                                |        |

| Figura 22: Espacio de trabajo inicial que entrega CadSoft Eagle para rutear las conexione    |        |

| componentes                                                                                  |        |

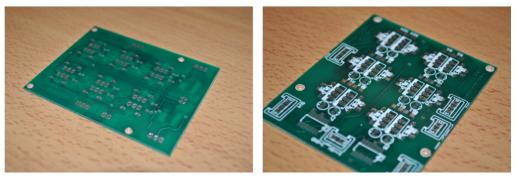

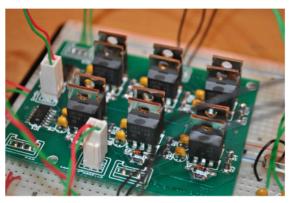

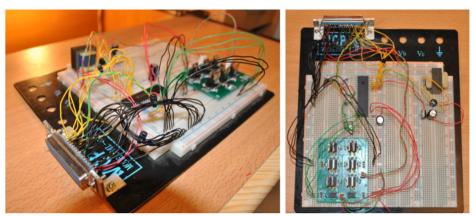

| Figura 23: Fotografías de la PCB del Pulser v.1.0                                            | 34     |

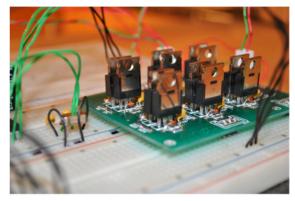

| Figura 24: Imágenes del montaje de componentes del Pulser v.1.0                              |        |

| Figura 25: Topología del Analog Switch ECN3290TF de HITACHI®                                 | 36     |

| Figura 26: Circuitos integrados de multiplexión ECN3290TF.                                   |        |

| Figura 27: Imagen que representa la identificación manual de pines del transductor           |        |

| Figura 28: Montaje para detección e identificación de posición geométrica de elementos       |        |

| Figura 29: Esquema de distribución de pines para el cabezal transductor.                     |        |

| Figura 30: Esquema de implementación para pruebas de multiplexión.                           |        |

| Figura 31: Fotografía del montaje de pruebas para decodificación de la multiplexión          |        |

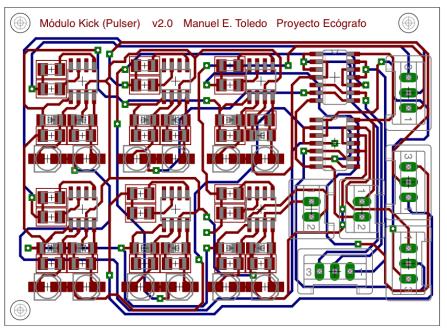

| Figura 32: Dibujo CAD de la placa para el sistema de pulsación Pulser v.2.0.                 |        |

| Figura 33: Imagen de la construcción y armado de la plataforma de pulsación Pulser v.2.0     |        |

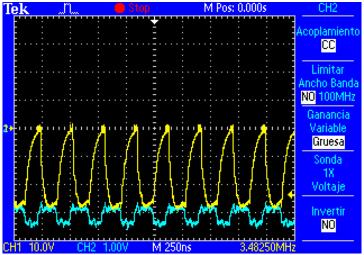

| Figura 34: Forma de onda para plataforma Pulser v.2.0.                                       |        |

| Figura 35: Plataforma MORPH IC de FTDI® para desarrollos en FPGA                             | 45     |

| Figura 36: Esquema básico del funcionamiento de la plataforma digital de control             |        |

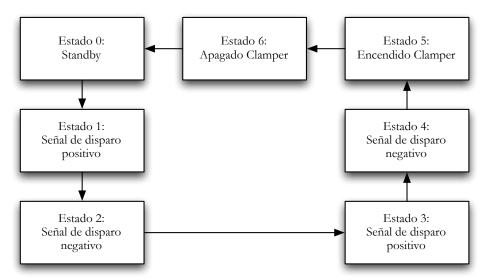

| Figura 37: Máquina de estados para el proceso de pulsación.                                  | 47     |

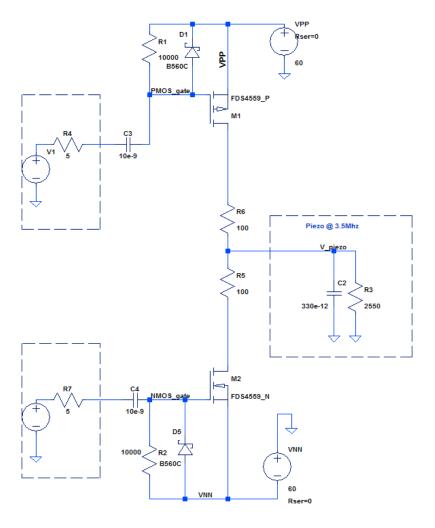

| Figura 38: Esquema de topología equivalente para simulación electrónica.                     | 48     |

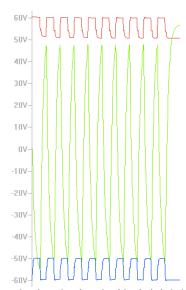

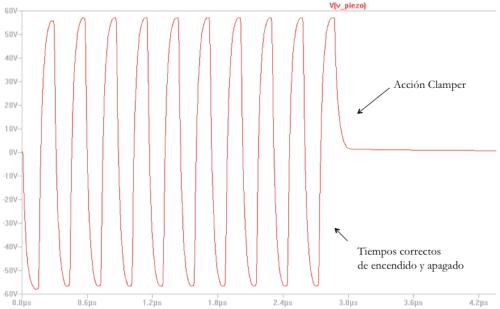

| Figura 39: Resultados de simulación inicial del Pulser v.2.5                                 |        |

| Figura 40: Corriente de drenaje vs. Tensión de compuerta para un MOSFET.                     |        |

| Figura 41: Resultados para nuevas resistencias de limitación de corriente.                   |        |

| Figura 42: Efecto de inercia presente en la carga piezoeléctrica.                            |        |

| Figura 43: Inclusión de sistema de clamping a simulación.                                    |        |

| Figura 44: Resultados obtenidos con la inclusión de un sistema de clamping.                  |        |

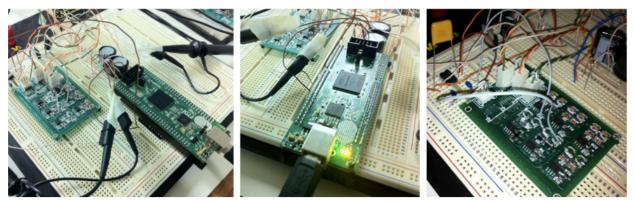

| Figura 45: Fotografías de implementación de la plataforma de pulsación Pulser v.2.5.         |        |

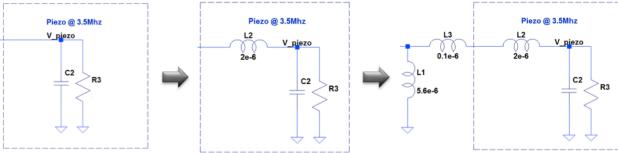

| Figura 46: Evolución del modelo electrónico equivalente del transductor ultrasónico          |        |

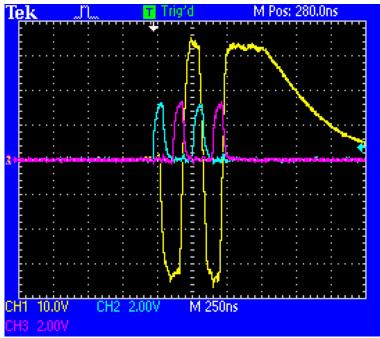

| Figura 47: | Resultados de pulsación y multiplexión con plataforma Pulser v.2.5.                | 55 |

|------------|------------------------------------------------------------------------------------|----|

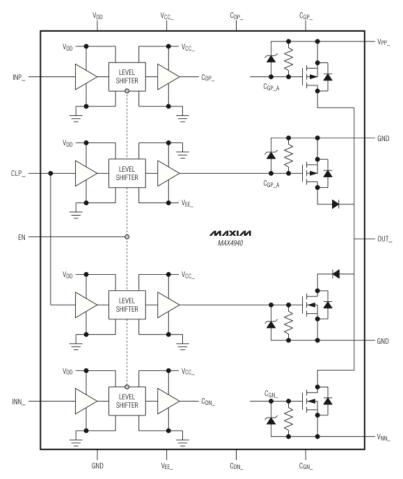

| Figura 48: | Diagrama funcional del IC de pulsación MAX4940A                                    | 56 |

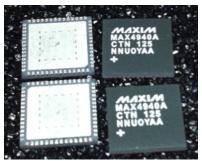

| Figura 49: | Fotografía del circuito integrado de pulsación MAX4940A                            | 57 |

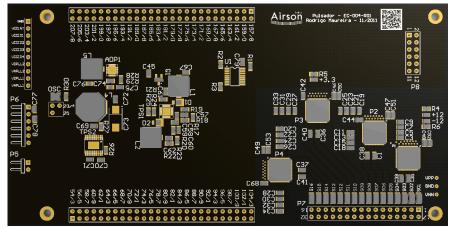

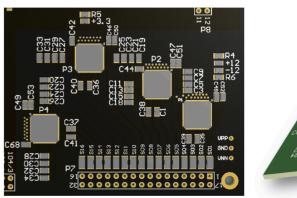

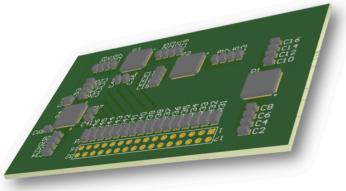

| Figura 50: | Vista preliminar del diseño CAD para el Pulser v.3.0.                              | 57 |

| Figura 51: | Fracción de la PCB correspondiente a la plataforma de la pulsación Pulser v.3.0    | 58 |

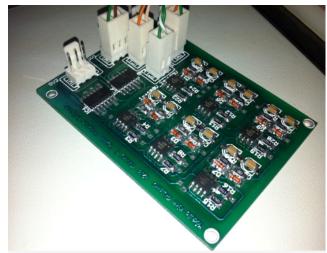

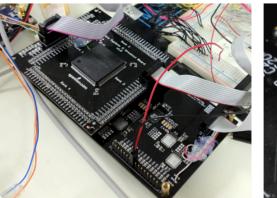

| Figura 52: | Fotografía de la implementación de la plataforma de pulsación Pulser v.3.0         | 58 |

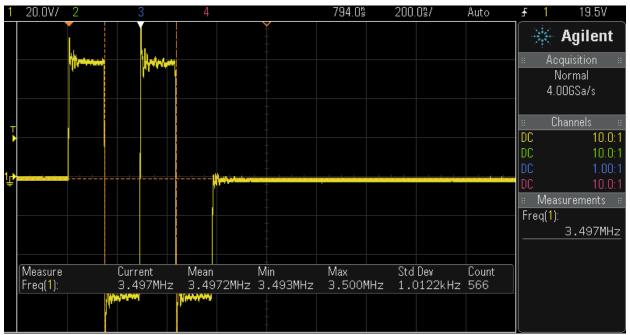

| Figura 53: | Prueba del sistema de pulsación Pulser v.3.0 con una carga resistiva               | 59 |

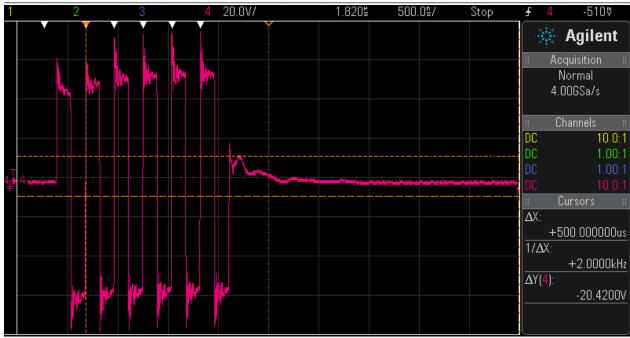

| Figura 54: | Prueba de pulsación para el Pulser v.3.0 con carga piezoeléctrica                  | 60 |

| Figura 55: | Resultados de pulsación para el Pulser v.3.0 con frecuencia de operación a 7 [MHz] | 60 |

| Figura 56: | Resultados de pulsación y recepción de ecos satisfactoria                          | 61 |

| Figura 57: | Fotografía de la plataforma de desarrollo ALTERA® DE2                              | 62 |

| Figura 58: | Esquema relacional de cores a desarrollar para interfaz digital de recepción       | 62 |

| Figura 59: | Captura de programa de recepción de datos en host                                  | 64 |

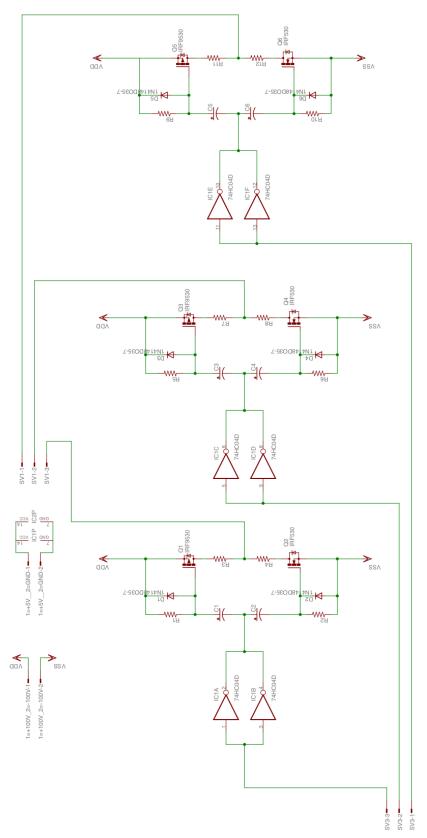

| Figura 60: | Detalle de un módulo de pulsación para la plataforma Pulser v.1.0.                 | 73 |

| Figura 61: | Esquemático general para la plataforma de pulsación Pulser v.1.0.                  | 74 |

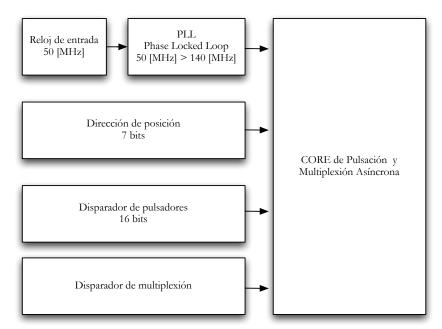

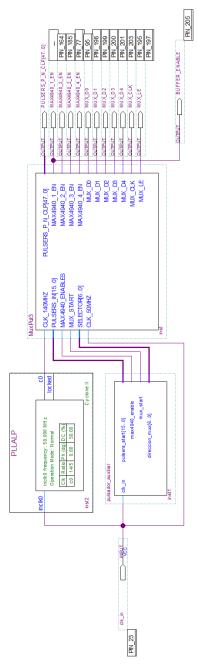

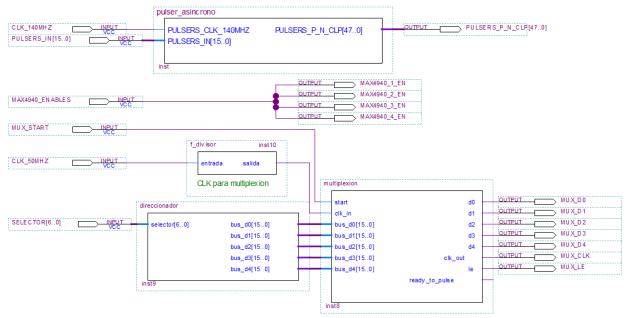

| Figura 62: | Diagrama de bloques global del sistema de multiplexión y pulsación asíncrono       | 76 |

| Figura 63: | Esquema funcional del módulo de interrelación y coherencia de datos                | 78 |

|            |                                                                                    |    |

# Capítulo 1

## Introducción

#### 1.1 Motivación

El acceso a exámenes de diagnóstico en los sistemas de salud chileno es muchas veces prohibitivo respecto de sus costos, efecto que se provoca por una demanda inelástica y además equipos y mano especializada extremadamente costosa. Particularmente, para el caso de Chile, todo el equipamiento es importado principalmente desde Estados Unidos y Europa, con marcas de alto prestigio que comercializan equipos de calidad, y que por lo tanto tienen costos muy elevados; esto hace que los equipos no estén en todos lados, por lo tanto para ofertas reducidas y demandas inelásticas, el parámetro que se dispara es el precio.

Hoy en día es fundamental, el acceso a exámenes que ayuden a la generación de un diagnóstico por el médico tratante, pero este tipo de procedimientos para los usuarios de la salud pública son lentos por la demanda de ellos en un sistema con oferta limitada. Por esta razón, los pacientes terminan esperando meses para hacerse un examen.

Aquí nace la idea del pre-diagnóstico, especialmente dada la estadística que señala, que del universo de exámenes de ultrasonido que se ejecutan, solo el 30% eran realmente necesarios; que pasaría entonces si se pudiera reducir ese 70% remanente. Una disminución de la demanda en ambos sistemas (público y privado), claramente reduce los costos por procedimiento.

La idea de este proyecto, se enmarca en suplir la necesidad de disponer de instrumental de pre-diagnóstico de bajo costo, orientado a generar información relevante en el primer examen del paciente. Así, se propone la construcción de un escáner de ultrasonido de bajo costo para examinación rápida, lo cual automáticamente permite tomar decisiones al médico respecto del paso siguiente en el tratamiento de un paciente. Por ejemplo, para un paciente que presenta aumento del volumen abdominal se puede asumir que:

- Es producto de acumulación de grasa

- Tiene un embarazo

- Acumulación anormal de líquido

Para un médico que no tiene acceso inmediato a equipamiento de imagenología, solo le queda enviar al paciente a realizarse el examen correspondiente; por otro lado, si éste tuviera acceso a un equipo de inspección rápida, podría desarrollar mucho mejor el siguiente paso y aliviar la demanda de los laboratorios de examinación detallada, como los departamentos de imagenología.

Además de ser un equipo de bajo-costo, este debe tener condiciones de portabilidad, de manera tal que pueda ser utilizado en servicios móviles de urgencia, salas de atención primaria, consultorios y hasta consultas particulares. En este contexto se propone el diseño de un ecógrafo ultra-portátil operado por baterías que pueda ser manejado por médicos que no sean necesariamente imagenólogos.

#### 1.2 Hipótesis de trabajo y metodología

Este trabajo postula que es posible implementar una plataforma integral de multiplexión, pulsación y recepción de señales ultrasónicas, en un dispositivo pequeño y de muy bajo-consumo basándose en los productos que actualmente se comercializan en el mundo. En este sentido, se dedicará especial cuidado a adoptar e implementar estrategias de diseño que eleven la eficiencia y permitan la miniaturización de los esquemas clásicos de construcción de ecógrafos.

Se utilizará la mayor cantidad de ingeniería aplicada posible, con énfasis en el empleo de circuitos integrados especializados en los diseños. Adicionalmente, se tendrá acceso a equipamiento de examinación ultrasónica funcional, para su respectivo análisis, permitiéndose incluso el desarme de estos para lograr una visión mucho más cercana a la filosofía de diseño que actualmente se utiliza en este tipo de equipos médicos. Finalmente, se buscará construir módulos electrónicos de alta densidad, que realicen las tareas antes mencionadas de forma específica, para más tarde poder integrarlos en una única solución de manejo de señales de ultrasonido.

### 1.3 Objetivos generales

En esta memoria se persiguen los siguientes objetivos generales:

- Análisis y puesta en marcha de un sistema de multiplexión estándar para un transductor de ultrasonido, logrando obtener el know-how para realizar el diseño y construcción de un multiplexor personalizado para la aplicación.

- Diseño y construcción de un módulo de pulsación de ultrasonido, que cumpla con los requerimientos de bajo-consumo y alta eficiencia impuestos por la portabilidad y operación desde baterías.

- Diseño e implementación del módulo digital de recepción de señales ultrasónicas para su posterior procesamiento.

## 1.4 Objetivos específicos

De los conceptos antes mencionados se pueden desprender los siguientes objetivos específicos:

- Investigación de topología y arquitectura electrónica utilizada para la realización de la multiplexión de forma activa en el transductor ultrasónico.

- Decodificación de la estructura de instrucciones para realizar un direccionamiento de multiplexión.

• Investigación los fenómenos y efectos generados, incluyendo las variaciones en los modelos electrónicos equivalentes, debida la inclusión de la multiplexión, el cable y el conector del transductor ultrasónico.

- Investigación del estado del arte en sistemas de pulsación para equipos de ultrasonografías médicas.

- Diseñar, simular e implementar una plataforma de pulsación operativa.

- Iterar sobre los diseños de la plataforma de pulsación para optimizar los consumos eléctricos, los tamaños y la eficiencia.

- Planificación de módulos digitales a diseñar, para importar datos obtenidos a alta velocidad hasta un computador host.

- Determinar la necesidad de inclusión de memorias de acceso aleatorio (RAM), para la captura de datos a alta velocidad.

- Diseñar medio de comunicación estándar para volcar los datos en un computador host.

#### 1.5 Estructura de la memoria

#### Capítulo 1: Introducción

Se muestra la motivación de la realización del proyecto, la hipótesis en la que se sostiene, la metodología de trabajo y los objetivos que este desarrollo persigue.

#### Capítulo 2: Fundamentos Generales

En este capítulo se expone el contexto teórico en el que se basa el trabajo a desarrollar, se investiga el estado del arte relacionado y se describe el aporte que este tiene.

#### Capítulo 3: Diseño e implementación de sistemas.

En esta sección se muestran los diseños y análisis realizados para lograr implementar una plataforma de pulsación y multiplexión funcional. Se incluyen optimizaciones como la inclusión de clampers a los módulos y la migración de los sistemas distribuidos a núcleos en una FPGA condensada.

#### Capítulo 4: Resultados, fabricación y pruebas de nuevas versiones, y desarrollos en recepción

En este capítulo se exponen los resultados obtenidos de la versión distribuida más operacional y se muestran los resultados de la última plataforma de pulsación implementada, la cual posee circuitos integrados dedicados para las tareas propuestas. Adicionalmente se documenta la generación de todo el módulo digital de recepción de señales ultrasónicas, el cual está basado en el diseño de núcleos para su implementación en una FPGA.

#### Capítulo 5: Conclusiones Generales y Trabajo Futuro

Se presentan las conclusiones del trabajo realizado, y las tareas que deben realizarse para concluir el diseño del producto final en contexto del proyecto.

# Capítulo 2

## **Fundamentos Generales**

En este capítulo, se introducirán los temas que fundamentan y contextualizan este trabajo de investigación y desarrollo. Hoy en día es imposible imaginar no contar con la disponibilidad de acceso a exámenes médicos, que permitan la visualización de órganos y tejidos mediante sistemas no invasivos y de fácil aplicación como son los ecógrafos. Sin embargo, en el presente se buscan más aplicaciones a este versátil método de examinación, como lo es la construcción de dispositivos ultraportátiles que permitan la ejecución de exámenes rutinarios de imagenología, pero en espacios reducidos y con un equipo energizado por baterías.

Estadísticamente se sabe que del total de las ecografías solicitadas; solo el 30% eran realmente necesarias, por lo tanto, la inclusión de equipos de rápido acceso y de categoría portable, es un eslabón deseable en el proceso de diagnóstico médico. De esta forma se plantea el diseño y fabricación de una plataforma electrónica que permita el manejo completo de un transductor ultrasónico para realizar la construcción de este tipo de dispositivos.

El problema que se abordará será el diseño e implementación de la electrónica requerida para la multiplexión, pulsación y recepción de datos de un transductor activo como arreglo de múltiples elementos piezoeléctricos. Dentro de este desarrollo se mantendrá un exhaustivo control del estado del arte en este aspecto, ya que no solo debe desarrollarse un sistema funcional, sino que adicionalmente se debe lograr miniaturizar todos los diseños para ajustarlos a los requerimientos de portabilidad. Es también de vital importancia, considerar la eficiencia de éstos y sus consumos respectivos, ya que el dispositivo no solo será portátil, sino que además será operado mediante baterías recargables, por lo que debe cumplir con ciertas restricciones mínimas de autonomía.

## 2.1 Funcionamiento básico de un equipo de ultrasonido

Un ecógrafo, es un equipo de uso médico que utiliza características específicas del fenómeno acústico para generar imágenes interpretables, donde se pueden visualizar tejidos y órganos, permitiendo de esta forma diagnosticar condiciones que no son identificables a simple vista. El equipo antes mencionado se basa en la condición física de reflexión de las ondas acústicas en medios materiales; en este caso, se produce un frente de ondas ultrasónico a través de un transductor

piezoeléctrico el cual es excitado a una frecuencia muy específica<sup>1</sup>, dependiendo de la arquitectura, geometría y prestaciones de cada sonda ecográfica. A partir de este momento, un frente de ondas acústicas penetra los tejidos del cuerpo, los cuales irán generando de forma coherente ecos, dependiendo de sus capacidades de reflexión y absorción, estos ecos vuelven al transductor, luego de un intervalo de tiempo directamente proporcional a la distancia del punto donde se reflejó la onda incidente.

El transductor genera entonces un trabajo mecánico el cual provoca la aparición de un frente de onda, luego este queda por unos instantes en estado de reposo, y a continuación debe recibir señales de ecos en magnitudes muy inferiores a las de emisión. Asumiendo una pequeña distancia, como es, la superficie del transductor y la zona muerta de éste, se puede estimar una distancia mínima de 3[mm], por lo tanto se recorrerá a lo menos 6[mm]; por otro lado, las máximas distancias que manejan los ecógrafos en general no superan los 250[mm], por lo que tenemos una cota superior de recorrido igual a 500[mm]. De esta forma se pueden calcular las magnitudes de tiempo que se deben manejar, para lograr capturar correctamente todos los ecos resultantes.

$$v_{sonido\ en\ tejidos} \cdot t = 2 \cdot d_{propagación}$$

$$\rightarrow t_{mín} = \frac{2 \cdot d_{propagación}}{v_{sonido}} = \frac{2 \cdot 3[mm]}{1540000[\frac{mm}{s}]} = 3.8961[\mu s]$$

$$\rightarrow t_{máx} = \frac{2 \cdot d_{propagación}}{v_{sonido}} = \frac{2 \cdot 250[mm]}{1540000[\frac{mm}{s}]} = 324.675[\mu s]$$

En el tiempo especificado se deben capturar las ondas resultantes, que son convertidas a señales eléctricas mediante los mismos transductores que antes emitieron el frente de ondas; estas señales eléctricas son 2 órdenes de magnitud más pequeñas que las de emisión, por lo que la arquitectura electrónica que debe manejar ambas magnitudes debe ser adecuadamente diseñada<sup>2</sup>. A continuación, se deben adquirir las señales para ser llevadas a un ambiente digital donde se puede aplicar todo el procesamiento para transformar señales crudas de eco en una imagen ultrasónica interpretable; la etapa de adquisición consiste fundamentalmente en conversores análogo-digital, de muy bajo ruido, gran profundidad de bits, pre-amplificadores incorporados, alta frecuencia de muestreo y una salida digital serializada de alta velocidad para el gran flujo de datos que se debe manejar.

Con los datos en formato digital, se procede al proceso de conformación, el cual está compuesto por las siguientes etapas:

- Se pre-filtra la señal con un filtro pasa-banda centrado en la frecuencia de pulsación, dejando así solo las componentes en torno a esta frecuencia, y atenuando el ruido y los artefactos.

<sup>2</sup> Nótese que las tensiones asociadas a la señal de emisión y recepción, las cuales distan en 2 órdenes de magnitud, están presentes en la misma ruta eléctrica.

<sup>&</sup>lt;sup>1</sup> El rango de frecuencias utilizadas para ultrasonografías médicas esta comprendido entre 1 y 10 [MHz]

- Considerando la forma y la inercia de las señales es posible realizar un proceso de upsampling, el cual se lleva a cabo introduciendo ceros intercalados en la señal y luego

filtrando la resultante con un filtro pasa-bajo, el cual se encarga de realizar una interpolación a la señal original, pero con una pseudo-frecuencia de muestreo mucho mayor.

- Con una matriz de retardos pre-calculada que introduce consideraciones geométricas y físicas respecto de cada elemento piezo-eléctrico, se pueden escoger estratégicamente datos de la señal, recuperando la frecuencia de muestreo original, pero con suficiente precisión como para calcular retardos en puntos no muestreados.

- Finalmente, se realiza un proceso de detección de envolvente, el cual es representable de forma directa en lo que se llama un "scanline" o línea de ultrasonido, la cual es visible en una ecografía como una línea vertical o descriptora de profundidad. Es un hecho que la aplicación de un algoritmo estándar de detección de envolventes no es suficiente para obtener imágenes de calidad media, lo que genera la necesidad de implementar esquemas más complejos como la Transformada de Hilbert.

La unión de estas líneas de forma secuencial una al lado de la anterior es finalmente el despliegue de la imagen; para un transductor de geometría lineal el posicionamiento de líneas adyacentes es representativo de la realidad, pero para un transductor convexo se debe realizar una conversión de coordenadas y aproximaciones de renderización¹ en base a interpolaciones bilineales, lo cual aumenta la complejidad de todo el problema de despliegue.

Figura 1: (Izquierda) Imagen original, (Derecha) Imagen procesada a través de un Scan Converter

En la Figura 1, se puede revisar la imagen obtenida luego de la etapa de conformación, pero sin la inclusión del efecto geométrico de que los datos fueron rescatados a través de un transductor ultrasónico convexo y no lineal; dado esto, se debe aplicar un algoritmo de cambio de coordenadas y renderización Scan Converter, el cual se encarga de generar una nueva imagen con las relaciones de aspecto y distancias correctas. Se debe señalar que la regeneración de esta imagen de forma adecuada², permite realizar mediciones en pantalla, que reflejan distancias reales en los tejidos examinados.

\_

<sup>&</sup>lt;sup>1</sup> Proceso de generar una imagen a partir de un modelo matemático.

<sup>&</sup>lt;sup>2</sup> Del aspecto de una imagen generada por un transductor lineal al de una generada por un transductor convexo.

Un esquema general de todo el proceso de captura de imágenes ultrasónico en grandes bloques funcionales se puede visualizar en la Figura 2.

Figura 2: Diagrama de bloques general de operación de un ecógrafo ultra-portatil

#### 2.2 Transductores ultrasónicos

Los transductores ultrasónicos para ecografías de examinación humana de hoy en día consisten, por lo general, en un arreglo unidimensional de piezoeléctricos equiespaciados que permiten el escaneo en una dimensión lateral y una dimensión de profundidad¹. En general, los arreglos son cantidades estándares de 80, 128, 192 y hasta 256 elementos; estas especificaciones permiten manejar la resolución axial de las ultrasonografías, esto dado que existen modelos de transductores con la misma excursión espacial, pero con distintas cantidades de elementos.

Figura 3: Transductor lineal de 4 cm. de excursión.

El transductor que se muestra en la Figura 3, corresponde a uno de geometría lineal con excursión de exploración de 4 cm; para este modelo, existen distintas arquitecturas de arreglos de piezoeléctricos, con versiones desde 80 hasta 256 elementos, esto implica que para la misma distancia de exploración se pueden obtener diversas resoluciones axiales.

Los ecógrafos tipo carro de examinación rutinaria, son por lo general equipos de gran tamaño que pueden tener soporte de hasta 6 transductores, con sus respectivos sistemas de interconexión. En este aspecto, todos los transductores ultrasónicos están conformados por 3 partes fundamentales:

- Empuñadura, donde se encuentra el arreglo de piezoeléctricos soportado por una estructura que permite su fácil manipulación y direccionamiento.

<sup>&</sup>lt;sup>1</sup> Generando por lo tanto, una imagen en 2 dimensiones.

- Cable, el cual por lo general tiene una medida de 1.5 metros, cumple con requerimientos de aislación eléctrica y además está compuesto de materiales de alta flexibilidad y resistencia para soportar el estrés de tracción y torsión al que está sometido diariamente.

- Conector, por lo general estructuras grandes y robustas, con inserciones de tipo ZIF¹, en las cuales se encuentran expuestas las conexiones de cada elemento piezoeléctrico(dos polos).

En el caso de un transductor ultrasónico lineal para examinación de baja penetración de 256 elementos, el conector posee un mínimo de 512 contactos, lo que lo hace fuertemente incompatible con aplicaciones portátiles, dado su gran tamaño y peso; en este sentido se deben hacer importantes adaptaciones al sistema tradicional de obtención de datos a través de una gran cantidad de celdas piezoeléctricas, migrándolo a un esquema donde se pueda negociar de forma eficiente el tamaño del conector y la cantidad de elementos disponibles en paralelo.

Figura 4: Transductor ultrasónico de 80 elementos, con conector convencional.

#### 2.2.1 Piezoeléctricos

Los elementos piezoeléctricos son dispositivos pasivos de materiales que son capaces de convertir ondas mecánicas en eléctricas y viceversa, fenómeno en el que esta basada la técnica médica de imagenología del ultrasonido. Estos elementos pueden ser sintonizados a frecuencias preestablecidas, dependiendo de los materiales de construcción, forma y su disposición geométrica.

Para el caso de los transductores ultrasónicos, estos se construyen conectados mecánicamente a un bloque de amortiguación el cual debe tener una impedancia acústica muy cercana al del material piezoeléctrico, ya que de esta forma se suprimen los fenómenos de resonancia y por lo tanto permite aumentar la fidelidad y ancho de banda del sistema. Adicionalmente, la arquitectura incluye una capa de protección y adaptación en el frente de éste, la cual asegura que se transmita la mayor cantidad de energía acústica desde el medio hacia cada elemento; por otro lado, también protege los transductores de daños mecánicos o químicos.

Respecto de la construcción, los materiales usados en los primeros años del ultrasonido como el cuarzo, sulfato de litio o el titanato de bario ya no son implementados hoy en día; en efecto, nuevos y más poderosos materiales están disponibles con características acústicas y eléctricas muy diversas. Este fenómeno se debe a que en el presente es posible generar compuestos cristalinos que

16

<sup>&</sup>lt;sup>1</sup> Zero Insertion Force, conectores que para su instalación solo deben ser puesto frente al placar de conexiones y luego girar un cerrojo que genera la fuerza para mantener unidas ambas partes.

posean características de sensibilidad, estabilidad y costo objetivo, por lo que es posible desarrollar un tipo de transductor para cada aplicación particular dependiendo de las restricciones del problema.

La gran masa de fabricantes de transductores para ultrasonografías generan sus dispositivos con Zirconato-Titanato de Plomo, el cual es una cerámica perovskita con grandes características piezoeléctricas y una incomparablemente alta eficiencia del 52%. Posee una de las impedancias acústicas más altas dentro del espectro de los piezocerámicos para frecuencias de resonancia menor a 25 [MHz], y es estable a temperaturas de operación de hasta unos 365°C.

Figura 5: Trozo de cerámica perovskita en bruto.

#### 2.2.2 Contextualización de los piezoeléctricos en el proyecto

Dadas las circunstancia industriales de fabricación presentes en Chile, no es posible contar con fabricantes de componentes y partes tan específicas como son los arreglos de piezoeléctricos para equipos de ultrasonografía. La fabricación de esta tecnología requiere de maquinaria muy especializada, la cual permite laminar de forma muy precisa estas cerámicas, logrando afinar su frecuencia de resonancia en la deseada para la generación de ondas ultrasónicas del espectro de interés.

De esta forma, se debió conseguir tecnología de fabricación en el extranjero para poder acceder a los transductores necesarios para el desarrollo del trabajo. En efecto, parte de las metas iniciales de este proyecto consistió en la generación de una cartera de contactos de donde adquirir este tipo de componentes.

La motivación a realizar esto, está fundamentada especialmente en la aceleración que recibe el proceso de investigación y desarrollo; ya que no solo se busca bibliografía y literatura asociada, si no que además se cuenta con la tecnología que actualmente se desarrolla, permitiendo dilucidar muchas interrogantes en un tiempo muy reducido.

Figura 6: Fotografía del cabezal piezoeléctrico utilizado.

En la Figura 6: Fotografía del cabezal piezoeléctrico utilizado. Figura 6 se puede visualizar una fotografía del cabezal transductor utilizado para el desarrollo de este trabajo, este consiste en un arreglo convexo unidimensional de 80 elementos piezocerámicos calibrados a una frecuencia de máxima sensibilidad en 3.5 [MHz]. Este transductor es uno de los más clásicos utilizados para examinación de órganos abdominales e incluso torácicos, ya que su penetración puede llegar a unos 25 [cm] de profundidad con resoluciones cercanas a 1 [mm].

En la imagen presente a la izquierda es posible notar las conexiones exteriores de cada elemento piezoeléctrico montados en un sustrato amortiguador, por otro lado en el lado derecho es posible visualizar la capa de adaptación acústica y protección contra daño mecánico y químico de color gris.

#### 2.3 Multiplexión

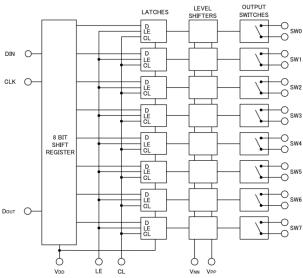

El proceso mediante el cual se puede tener acceso a un conjunto amplio de canales a través de un número reducido de estos mismos, se llama "multiplexión"; este consiste en una topología electrónica donde se seleccionan las señales entrantes mediante un bus selector, el cual indica que parte de la entrada se transmitirá por los canales de salida (Figura 7).

Figura 7: Esquema básico de funcionamiento de un multiplexor.

Este procedimiento es realizado electrónicamente mediante transistores MOSFET, funcionando en modo de corte y saturación como interruptores. La idea principal consiste en 2 capas fundamentales: la primera corresponde al arreglo de transistores que permiten hacer converger todas las señales deseadas a un bus de ancho definido, los cuales se disponen de forma óptima para lograr impedancias de interrupción iguales en todos los canales; la segunda etapa, corresponde al control de estos transistores, es decir, las señales que encienden o apagan cada bifurcación para hacer llegar la señal entrante al puerto de salida deseado. Por lo general esta capa de control no es un selector de entrada paralela, sino que por lo general son entradas serializadas que permiten realizar configuraciones de varios bits en solo un pin de entrada del encapsulado. La arquitectura de manejo de este tipo de configuraciones es un *stack* FIFO¹, por lo tanto se deben ingresar los bits de forma ordenada y síncrona a través de un reloj, el cual en cada flanco de subida empuja un dato nuevo al

<sup>&</sup>lt;sup>1</sup> FIFO: Sistemas de encolamiento First-In-First-Out, donde el primer elemento que entra al arreglo, es el primero que sale.

arreglo; finalmente cuando el dato está completamente determinado y posicionado en el buffer interno de la etapa de control, se genera un flanco de bajada en una señal de "latch" para entregar este bus de datos estabilizados a la etapa de disparo de los transistores. Todo lo mencionado implica directamente que se debe incorporar una maquinaria completa de lógica electrónica, para lograr operar el selector de multiplexión, y por supuesto también, las señales necesarias para la pulsación.

Finalmente se debe considerar que este tipo de sistemas de multiplexión e interrupción deben tener resistencias de conexión muy bajas, pues deben adaptar señales de gran excursión como son los pulsos ultrasónicos, los cuales operan entre +100[V] y -100[V]; y por otro lado, otorgar mínima atenuación a los ecos de retorno, los cuales son unas 100 veces más pequeños que las señales de pulsación.

#### 2.3.1 Contextualización de la multiplexión en el proyecto

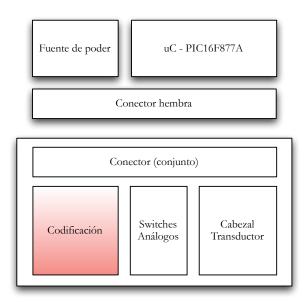

Dados los proveedores disponibles se adquirió un transductor completo, lo que implica el cabezal transductor, la empuñadura, el cable de conexión y el conector principal. El transductor especificado no es pasivo, es decir, posee electrónica que realiza labores de multiplexión en el mismo dispositivo.

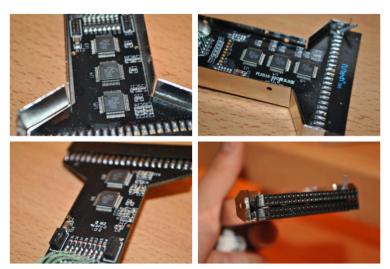

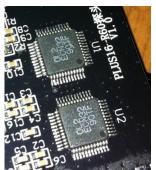

Figura 8: Fotografías de la situación interna del transductor ultrasónico.

En la Figura 8 se muestra la situación del interior del transductor, particularmente en la zona de la empuñadura de la sonda, donde se albergan las tarjetas electrónicas.

Si bien, este hecho genera grandes ventajas respecto al aumento en la velocidad del desarrollo dado que se tiene un transductor activo con multiplexión listo para operar, se tiene la gran desventaja que implica no tener información respecto del funcionamiento y la arquitectura, ya que son dispositivos de consumo ya producidos que justamente intentan proteger sus diseños, ocultando su funcionamiento interno.

19

<sup>&</sup>lt;sup>1</sup> Esquema asíncrono clásico de electrónica digital que permite guardar de forma estable un dato entrante en un cierto instante.

Se apuesta entonces a la decodificación de la arquitectura y las comunicaciones para poder usar este dispositivo como instrumento, sin tener que estar re-fabricándolo con tecnología mas cara y escasa. Esto constituirá también, uno de los desafíos que incluye este trabajo en su desarrollo.

#### 2.4 Pulsación

Esta etapa consiste en la generación de pulsos ultrasónicos a nivel eléctrico correctamente adaptados, logrando de esta forma excitar de forma adecuada cada elemento piezoeléctrico en el arreglo. Este corresponde a un proceso no-trivial, ya que se deben generar pulsos de más de 1 [MHz] de frecuencia con niveles de excursión de hasta 200 [Vpp], esto genera directamente dos temáticas asociadas: en primer lugar, se deben realizar diseños con transistores de muy baja capacitancia de compuerta y grandes niveles de tensión drenador-fuente; por otro lado se deben incluir drivers de bajos tiempos de propagación y altas corrientes de salida, las cuales alimentarán las compuertas de los MOSFETs.

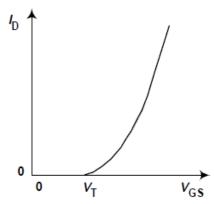

#### 2.4.1 Transistores MOSFET para conmutación

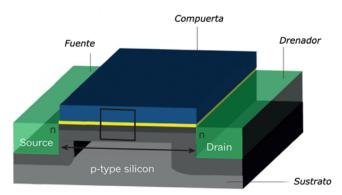

Los transistores que se utilizan para fines de pulsación son deseablemente pequeños, esto es dados los beneficios físicos electrónicos que tiene en este tipo de aplicaciones. Un modelo muy clásico de los transistores MOSFETs es la vista como un interruptor semi-conductor con una compuerta aislada y que tiene características de capacitor, esto es dado que si se aplica un voltaje positivo<sup>1</sup> a la compuerta, se estará creando un campo eléctrico entre esta y el resto del sustrato del transistor; cuando la tensión aplicada en la compuerta es suficientemente alta para superar la barrera de potencial generada por el sustrato tipo P, se genera un canal de conducción, apareciendo un flujo de corriente desde el drenador (drain) hacia la fuente (source), generando un camino de baja impedancia que se asocia a un interruptor cerrado.

Figura 9: Modelo Físico Electrónico de un transistor MOSFET.

El modelo antes mencionado es representable mediante capacitancias<sup>2</sup>, particularmente se puede establecer que la tensión "gate-source"  $V_{gs}$  va directamente relacionada con el campo eléctrico producido, a su vez la tensión  $V_{as}$  es proporcional a la resistencia de conducción y por lo tanto a la condición de encendido del transistor. Si esta curva se recorre lentamente, se generarán grandes pérdidas por conmutación, dado que la tensión "drain-source"  $V_{DS}$  instantánea será considerablemente alta, la cual es directamente proporcional con la potencia disipada sobre el transistor; este efecto no

<sup>2</sup> Particularmente por los fenómenos electrostáticos presentes.

<sup>&</sup>lt;sup>1</sup> En este caso a un transistor MOSFET canal N

es deseable y se puede evitar recorriendo la curva de carga muy rápido. Se conoce la ecuación de corriente como:

$$I = \frac{q}{t}$$

donde "q" corresponde a la carga inyectada y "t" el tiempo que toma, luego si se desea mover grandes cantidades de carga en un tiempo reducido, una forma directa de realizarlo es aumentar la corriente impuesta a la compuerta. Para esto se requiere de una fuente de corriente controlada electrónicamente que permita encender rápidamente el transistor en cuestión por un tiempo preestablecido.

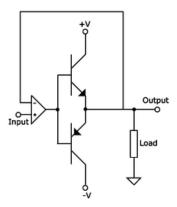

El concepto de fuente de corriente electrónicamente controlada antes mencionado, se puede implementar mediante un MOSFET driver, el cual en estricto rigor corresponde a un dispositivo que entrega corriente en términos de una entrada digital. Estos por lo general consisten en un arreglo de transistores dispuestos en configuración "push-pull", la cual mediante dos transistores conectados en serie es capaz de entregar corriente y absorber corriente.

Figura 10: Circuito clásico de configuración push-pull.

Según se menciona anteriormente, es de suma importancia inyectar carga de forma muy rápida en la compuerta, ya que de esta manera es posible encender en corto tiempo el transistor, evitando así pérdidas por conmutación y sus ineficiencias e inestabilidades asociadas; de esta misma forma, es también vital poder apagar rápidamente el MOSFET. Esto es realizado mediante la absorción o drenaje de corriente desde la compuerta, lo cual es directamente logrado habilitando un camino de baja impedancia entre la compuerta y su nodo de referencia a la fuente del transistor. Con esta configuración driver-mosfet, es posible controlar de forma eficiente el encendido y apagado del transistor con una señal de carácter digital, la cual será comandada desde la plataforma de procesamiento.

#### 2.4.2 Estado del arte de los sistemas de pulsación

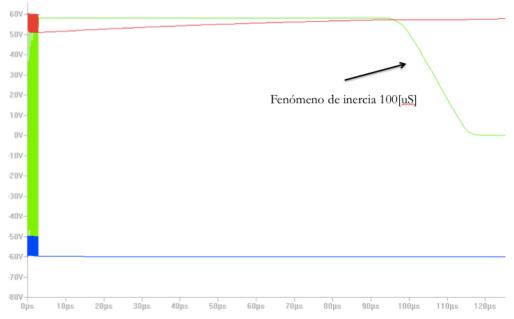

Con estos antecedentes es posible hacer un análisis del estado del arte respecto a pulsación de ultrasonido, donde se generan otros fenómenos que deben ser analizados, particularmente dadas las características eléctricas del modelo del cristal piezoeléctrico.

La arquitectura planteada, compuesta por un *pulser* basado en transistores MOSFET, un sistema de driving para el encendido eficiente y su correspondiente transductor, es la más básica, y es llamada arquitectura de "*pulser* unipolar". Tal como se menciona en Haider 2006[1]¹, el elemento piezoeléctrico se puede modelar como un capacitor, por lo tanto este se carga cuando es energizado por el sistema de pulsación. La desventaja que presenta este hecho es que cada elemento tiene un comportamiento capacitivo y por lo tanto tiempos de respuesta perturbados por las distorsiones en frecuencia y en fase que generan cargas pasivas con estas características. En efecto, tal como se menciona en la publicación, la mayoría de los sistemas de pulsación unipolares existentes deben usar sistemas de drenaje para lograr un comportamiento adecuado.

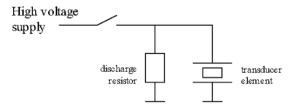

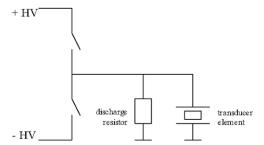

Figura 11: Esquema de pulsación unipolar clásico usado.

La necesidad de inclusión de la resistencia de descarga tiene un único sentido, y es quitar inercia a la carga del sistema de pulsado. Este fenómeno se requiere, ya que si bien la generación y desvanecimiento del canal de conducción del transistor MOSFET es dependiente de la cantidad de carga electrostática presente en la compuerta, es también fundamental, para que se cumpla esta dinámica, que exista una carga  $R_L$  correctamente adaptada en la salida del transistor. Esto efectivamente no se cumple con cargas tan capacitivas como un elementos transductor ultrasónico, por lo que la única forma de adaptarlo de forma pasiva es agregando un sistema de drenaje.

El problema que conlleva esta solución es que, si bien efectivamente se cumple el requisito, es un sistema altamente ineficiente. Esto dada la diferencia abismante de impedancias en régimen de corriente continua presentes; por un lado el modelo de impedancia equivalente del transductor ultrasónico a 3.5 [MHz] es de aproximadamente 2 [k $\Omega$ ] resistivos en paralelo a una capacitancia de 300 [pF], equivalente a una impedancia de 952 [ $\Omega$ ] a la frecuencia antes mencionada; por otro lado, en cambio, la resistencia de drenaje para una operación correcta, debe ser de valores cercanos a los 25 [ $\Omega$ ]. Así es posible realizar de forma directa el siguiente cálculo en régimen de operación.

$$I_{transductor} = \frac{100 \ [V]}{2000 \ [\Omega] - j \cdot 952 [\Omega]} = 0.0411 + 0.01905 \cdot j \ [A]$$

$$\rightarrow |I_{transductor}| = 0.04538 \ [A]$$

Por otro lado, si calculamos la corriente circulante en el conjunto paralelo:

$$\begin{split} I_{conjunto} &= \frac{100 \ [V]}{(2000 \ [\Omega] - j \cdot 952 [\Omega]) \ || \ 25 [\Omega]} = 4.04118 + 0.019050 \cdot j \ [A] \\ &\rightarrow \left| I_{conjunto} \right| = 4.04123 \ [A] \end{split}$$

<sup>&</sup>lt;sup>1</sup> B. Haider, "Power Drive Circuits for Diagnostic Medical Ultrasound", 18th International Symposium on Power Semiconductor Devices & IC's, Naples, Italy, June 2006.

Es posible concluir que la corriente del conjunto es una 100 veces mayor a la del transductor de forma aislada, esto implica que casi el 99% de la energía esta destinada a alimentar la resistencia de drenaje y no el elemento que se busca energizar. Si bien, esto funciona y permite un apagado rápido de los transistores de pulsación, es un esquema que desperdicia mucha energía, la cual es valiosa en

equipos e implementaciones portátiles.

La configuración antes mencionada es utilizada en aproximadamente el 20% de los sistemas de ultrasonido, ya que permite desarrollar arquitecturas electrónicas muy sencillas y funcionales, sin embargo, presenta una gran desventaja respecto de la sub-utilización de la excursión total de cada elemento transductor. Los elementos piezoeléctricos poseen un estado de régimen permanente en el cual su deformación es nula y por lo tanto su tensión lo es también, pero dada la naturaleza elástica encontrada, el fenómeno es simétrico respecto del estado de reposo, lo que implica que la excursión máxima es alcanzada cuando se lleva a estados de máxima-compresión y máxima-tracción. Este efecto mecánico en términos eléctricos, corresponde a la aplicación de tensiones positivas y negativas al sistema piezocerámico, por lo que al adoptar una arquitectura con fuentes unipolares, solo estaremos usando una fracción de la excursión máxima del transductor.

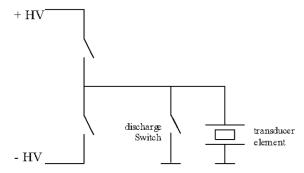

Dado lo anterior, es que el 70% del mercado de los equipos de ultrasonido usa la siguiente estructura electrónica para sus sistemas de pulsación.

Figura 12: Arquitectura electrónica de un pulser bipolar.

En este caso claramente se alimenta el transductor con tensiones positivas y negativas, lo que genera directamente mayor excursión, ondas más estables y por lo tanto ecos de mejor calidad y amplitud. Aún así, el sistema sigue incluyendo una resistencia de drenaje que otorga bajísimas eficiencias al sistema, que para la gran masa de equipos comercializables no es un problema, ya que operan conectados directamente a la red eléctrica del recinto.

Así y dadas todas las condiciones anteriores, en [1]<sup>1</sup> se sugiere una nueva arquitectura que usan los fabricantes más innovadores y que efectivamente maneja esta gran ineficiencia.

<sup>&</sup>lt;sup>1</sup> B. Haider, "Power Drive Circuits for Diagnostic Medical Ultrasound", 18th International Symposium on Power Semiconductor Devices & IC's, Naples, Italy, June 2006.

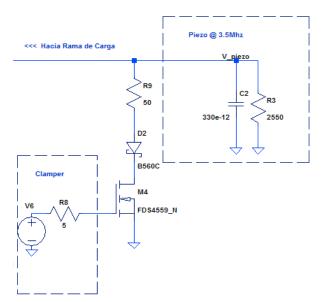

Figura 13: Topología de pulsación con clamper.

El objetivo en este esquema es incluir la resistencia de drenaje, solo cuando ésta es necesaria, es decir, en la etapa de apagado; particularmente se establece una conexión de descarga de forma controlada por una fracción muy pequeña de tiempo justo después del término de la última señal de pulsación.

Para esto se utiliza una arquitectura, como la mostrada en la Figura 13 donde en paralelo al transductor piezoeléctrico (de la misma forma que estaba conectada la resistencia de drenaje), se conecta un transistor de conmutación, que permitirá generar de forma controlada un camino de baja impedancia cuando se desee eliminar la inercia inherente del sistema capacitivo del piezoeléctrico.

La idea fundamental detrás la revisión de este modelo, es que este esquema sea simulado, para probar su implementabilidad, y si es factible la construcción de un circuito de esta categoría, entonces se tendrán reducciones sustanciales en el consumo basal del sistema de pulsación de ultrasonido, siendo esto un interesante resultado dentro del desarrollo de la memoria; particularmente dadas las condiciones de portabilidad implicadas en este proyecto.

#### 2.4.3 Contextualización de la pulsación en el proyecto

Las arquitecturas utilizadas en el equipo que se inspeccionó para la fluidez del desarrollo de la investigación, no cumplían con los requisitos de tamaño, consumo y eficiencia que el planteamiento inicial de portabilidad consideraba, por lo tanto se descartó su análisis para así abrir camino a una amplia línea de investigación, diseño, desarrollo e implementación que efectivamente corresponde a uno de los objetivos fundamentales de esta memoria.

Para los desarrollos se comienza la investigación a partir de notas de aplicación y uso de componentes electrónicos específicos para la generación de pulsos ultrasónicos de examinación médica, donde se presenta una opción proveniente de Estados Unidos respecto a fabricación de circuitos integrados para su uso en la construcción de ecógrafos. La ventaja corresponde en este caso, a un fabricante que entrega diseños de arquitecturas para la implementación de sistemas de pulsación y recepción de señales ultrasónicas médicas.

Figura 14: Arquitectura de pulsación propuesta en las notas de aplicación de Supertex® Inc.

Acceder a esta información resulta útil, pues entrega datos importantes respecto de la arquitectura y las consideraciones que se deben tener al diseñar un sistema de pulsación ultrasónica. Particularmente la propuesta de Supertex®¹ consiste en una aplicación basada en transistores MOSFET en configuración "push-pull", sus respectivas etapas de disparo con levantadores de referencia, y sistemas de protección y drenaje para la carga equivalente al cristal piezoeléctrico. Estos planteamientos permiten consolidar algunos conceptos y mejorar las hipótesis de planificación de diseño, por ejemplo la inclusión de una resistencia de drenaje es decidor respecto de las arquitecturas usualmente utilizadas y como estas son implementadas en equipos vigentes.

Figura 15: Arquitectura Propuesta por National Semiconductor ®.

En la Figura 15, ya es posible ver la inclusión de sistemas de clamper que permiten el drenaje eficiente de las corrientes almacenadas temporalmente en los cristales ultrasónicos, sin embargo es considerado como un accesorio y sigue viéndose la presencia de resistencias pasivas de adaptación de carga. Respecto de la etapa de potencia, esta se considera del tipo "push-pull", con toda la maquinaria previa que permite su correcto funcionamiento.

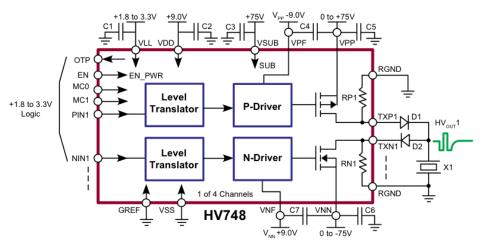

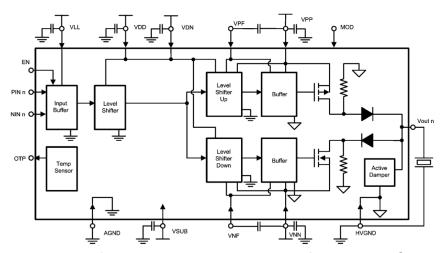

Dentro de la investigación se identifica un componente de estado-del-arte de la pulsación para ecógrafos desarrollado por la compañía MAXIM Integrated Products® el cual cuenta con todas

<sup>&</sup>lt;sup>1</sup> Información disponible en www.supertex.com

\_\_\_\_\_

las prestaciones esperadas por el equipo a desarrollar, sin embargo al ser un componente de categoría "prototipo", debe ser lanzado y puesto a disposición, para luego comercializarlo, por lo que la disponibilidad de este circuito integrado es incierta. Aún así se abre una hebra de trabajo donde se incluye el circuito integrado MAX4940¹ como solución integral del problema de pulsación. Así mismo, se enrutan los diseños a realizar con esta concepción, ya que cumple las restricciones del problema y además posee grandes muestras de ser un esquema óptimo para la solución que se pretende desarrollar.

#### 2.5 Conector

Aunque pudiese parecer poco importante, uno de los flancos a atacar en el contexto de este proyecto es la miniaturización del sistema que conecta el transductor a través de su cable con el equipo propiamente tal.

El estándar de los transductores ultrasónicos es fabricado para escáneres de ultrasonografía estacionarios, los cuales además de estar conectados a la red eléctrica del recinto permanentemente, también tienen mucho espacio para el hardware, puesto que su arquitectura es muy similar a la de un mueble. Esto implica por lo general que los ecógrafos tienen hasta 8 entradas para distintos transductores con distintas geometrías y frecuencias de operación, lo cual ocupa espacios considerables, ya que en función de mantener las mejores resoluciones posibles, no existe etapa de multiplexión y por lo tanto los elementos se encuentran uno a uno alambrados hasta el equipo de ultrasonido; así, suponiendo un transductor clásico de 128 elementos, el conector tendrá a lo menos 256 pines que deben tener una distancia considerable para su correcto funcionamiento y aislación de alta tensión. Estas características hacen que los transductores convencionales para ecógrafos estacionarios tengan tamaños de magnitudes como : 12 [cm] x 10 [cm] x 6 [cm]; algo absolutamente inviable para los diseños planificados, pues la idea es que el producto final completo tenga dimensiones similares a esas.

Este problema fue resuelto mediante la utilización de transductores construidos para equipos portátiles los cuales incluyen multiplexión y por lo tanto, el cable y su conector son varias veces más pequeños.

Figura 16: Comparativa de tamaños para los conectores de transductores.

En la Figura 16, se puede ver a la izquierda solo el frontal de un conector para un transductor pasivo de ecógrafo estacionario, al cual aún le falta el ensamblado de el chasis de éste el cual es metálico, pesado y muy grande; en el lado derecho de la figura es posible ver el conector de un

<sup>&</sup>lt;sup>1</sup> Dual/Quad, Unipolar/Bipolar, High-Voltage Digital Pulsers (www.maxim-ic.com)

transductor activo y multiplexado, el cual fue diseñado para un ecógrafo portátil tipo "laptop" y que tiene dimensiones muy inferiores, del orden de : 5 [cm] x 4 [cm] x 1.2 [cm].

Finalmente, cabe mencionar que no solo tiene ventajas respecto de los tamaños, si no que además el hecho de ser de procedencia China, hace que el costo del conjunto transductor, cable, conector; sea una diez veces menor. Este hecho, determina la conveniencia de usar la sonda tal como viene desde el origen.

#### 2.6 Etapa de adquisición de señales

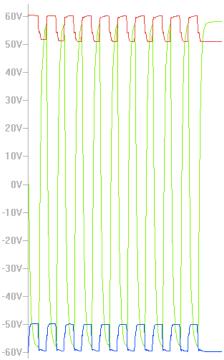

Una vez que los pulsos de alta tensión se disparan desde los piezoeléctricos, estos viajan por los tejidos y rebotan generando ecos que volverán eventualmente al transductor, estos ecos ultrasónicos deben ser capturados, ya que son las señales que poseen toda la información del entorno, incluyendo densidades y profundidades. El proceso de adquisición analógica es algo directo una vez que se tiene implementada la multiplexión, pero también se debe realizar la conversión digital y la captura de estos datos.

El sistema completo posee a lo menos 80 elementos piezoeléctricos, los cuales serán multiplexados, escogiendo 16 del conjunto completo; los datos provenientes de estos 16 elementos deben ser capturados, convertidos y procesados en tiempos del orden de los milisegundos, ya que esto se debe realizar varias veces tal que se recorra el total de los elementos. Adicionalmente se necesita reiteración puesto que las imágenes de ultrasonido son en tiempo real, y por lo tanto las imágenes se deben refrescar de forma periódica y frecuente de modo tal que se pueda generar el efecto de video.

Las 16 señales que se reciben en paralelo deben ser convertidas a datos digitales de alta precisión con 12 bits de resolución, y además se deben capturar varias miles de muestras en cada disparo, pues estas dirán donde están los obstáculos que encontró el frente de ondas ultrasónicas emitido. Todo este enorme caudal de información debe ser llevado hasta la plataforma digital escogida, para poder realizar la conformación. En efecto, los flujos de información son suficientemente grandes como para impedir la utilización de plataformas de procesamiento secuenciales como micro-procesadores, en su defecto, se hace uso de sistemas de procesamiento paralelo como son las FPGAs. Adicionalmente, se debe contar con esquemas electrónicos de comunicación adecuados para este flujo de datos, como lo son los pares diferenciales LVDS, los cuales serán expuestos más adelante.

#### 2.6.1 FPGA

Las FPGAs (Field-Programmable Gate Array) son circuitos integrados diseñados para ser configurados y programados por los desarrolladores. Estas son configuradas a través de lenguajes de descripción de hardware¹ y son usadas para implementar cualquier tipo de función lógica que un circuito integrado de aplicación específica (ASIC)² pueda realizar. Sus grandes ventajas corresponden a la factibilidad de cambiar su configuración y funcionalidades, y por su puesto a las cualidades de procesamiento paralelo que puede lograr.

\_

<sup>&</sup>lt;sup>1</sup> HDL: Hardware Description Language.

<sup>&</sup>lt;sup>2</sup> ASIC: Application-Specific Integrated Circuit.

Estos dispositivos contienen lógica programable basada en los llamados "elementos lógicos", y una jerarquía de interconexiones reconfigurables que permiten a los bloques comunicarse entre ellos; de esta forma estos bloques lógicos pueden ser agrupados para conformar funciones combinacionales complejas o sistemas de memoria volátil.

Estos circuitos integrados, no solo se usarán en las etapas de adquisición y procesamiento, sino que además se implementarán desarrollos en FPGAs para la etapa de pulsación y multiplexión, particularmente para las señales de control digital que estos bloques funcionales requieren. Algunas de las razones por las cuales se genera este concepto, es por su gran versatilidad y las capacidades de optimización de energía, dada la naturaleza de dispositivos dedicados que estos tienen.

Figura 17: Encapsulado FPGA que se usará para los desarrollos.

#### 2.6.2 Pares diferenciales LVDS

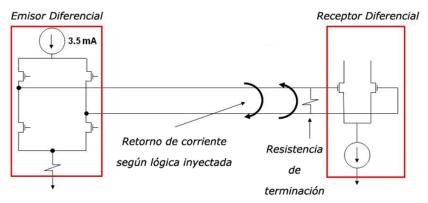

Los pares diferenciales LVDS (low-voltage differential signaling) son un estándar de transmisión de señales digitales, que puede lograr grandes velocidades de transferencia a través de medios de muy bajo costo como los pares trenzados de cobre. El hecho de que sean diferenciales implica que transmite información como la diferencia de dos voltajes en un par de conductores, lo cual es logrado mediante la incorporación de una resistencia de aproximadamente  $100 \ [\Omega]$ , adaptada a la impedancia característica del cableado en el terminal receptor del sistema. Esta topología electrónica permite que el receptor interprete la polaridad de este voltaje (dado que es diferencial), para determinar el nivel lógico correspondiente.

Sin embargo, los pares diferenciales no solo se pueden implementar en medios como pares trenzados de cobre, sino que además se pueden incluir en diseños de circuitos impresos (PCB¹) mediante pistas paralelas, de largos, anchos y espesores correctamente calculados. Es el esquema que se llevará a cabo para la comunicación entre los conversores Análogo/Digital y las FPGAs, fundamentalmente dada la gran cantidad de información digital libre de ruido que se requiere adquirir. Un cálculo rápido nos permite percibir la magnitud de estos flujos:

$16 \ elementos \cdot 40 \ MSPS \cdot 12 \ bits = 0.89406 \ [GBps]$

28

<sup>&</sup>lt;sup>1</sup> Printed Circuit Board.

donde MSPS corresponde a millones de muestras por segundo y 12 bits la resolución de cada muestra. Esta aproximación es suficiente como para enfrentar la situación de transmisión con la

importancia que esta realmente tiene.

Adicionalmente, el ambiente donde estarán presentes estas señales, corresponde a uno lleno de ruidos pulsantes que generan incertidumbre respecto de la integridad de los datos; es por esto que la idea de usar un sistema de transmisión LVDS toma validez, ya que las interferencias eléctricas y magnéticas a las que está sujeto un conductor del par diferencial, son muy parecidas a las de su opuesto, por lo que al restar ambas señales, el ruido superpuesto en ambas es eliminado por completo.

Figura 18: Esquema de funcionamiento para un sistema de transmisión LVDS.

#### 2.7 Etapa de procesamiento de señales

La capa visible para cada usuario de un escáner de ultrasonografía, es efectivamente la etapa de visualización, la cual viene precedida por una sección importante de procesamiento, la cual se encarga de tomar un arreglo de posiciones rescatadas a través de los ecos y formar una imagen interpretable y con escalas coherentes.

La primera etapa justo después de la conformación de ondas, corresponde a filtros de atenuación de ruido e intensificación de bordes, los cuales son ampliamente útiles en este aspecto, dado que permiten una lectura más rápida y eficiente de lo que efectivamente está siendo recibido a través del transductor ultrasónico. La idea detrás de esto consiste en la mejora de las imágenes media post-procesamiento convencional de imágenes el cual por lo general esta compuesto de filtros pasabajos o pasa-banda, incluyendo algunos de algoritmos locales como medias móviles o convoluciones de detección de bordes.

La implementación de estos filtros es realizada por lo general en plataformas de procesamiento de señales digitales como los DSPs¹, los cuales poseen librerías y funciones preconfiguradas para el tratamiento de imágenes; en efecto, estos dispositivos están muy bien desarrollados y optimizados para este tipo de funciones, sin embargo poseen algunas consideraciones respecto de la energía, y es que si se desean realizar tareas como las antes mencionadas, las plataformas sugeridas, tienen velocidades de núcleo cercanos a los 1.2 [GHz], lo que implica de forma directa grandes consumos energéticos en pérdidas por conmutación, llevando la electrónica a temperaturas cercanas a los 60°C.

-

<sup>&</sup>lt;sup>1</sup> Digital Signal Processor.

En el contexto del proyecto, particularmente para el caso de la implementación de un equipo ultra-portátil, esto no se ajusta a los requerimientos básicos, los cuales consideran sistemas de bajo consumo y los más eficiente posible. Dado esto se debe optar por la implementación de estos algoritmos basados en FPGAs, las cuales pueden realizar procesamiento paralelos a algunos cientos de Mega Hertz, en vez de procesamiento secuencial a Giga Hertz; adicionalmente es posible controlar el encendido y apagado de relojes de alta velocidad temporalmente, según se requiera para optimizar aún más los consumos asociados.

#### 2.8 Dominio y aporte del trabajo

Se espera como aporte diferenciador para este trabajo, la generación de una plataforma de pulsación ultrasónica de dimensiones muy reducidas y de bajos consumos, para su implementación en la construcción de un ecógrafo ultra-portátil. En el aspecto de innovación tecnológica a nivel nacional y latinoamericano es un concepto novedoso con un mercado atractivo, y con desarrollo muy escaso. En particular se busca la generación de un sistema de pulsación clasificable como estado-delarte con la inclusión de tecnologías como el *clamping* activo y capacidades de pulsar a frecuencias de hasta unos 7.5 [MHz]. Adicionalmente y como un plus-valor importante se buscará integrar este concepto con sistemas de multiplexión activa de administración abstracta; lo que se puede considerar una etapa completa de emisión-recepción de ondas ultrasónicas análogas, las cuales irán mas tarde al mecanismo de conformación.

Respecto del dominio y los alcances, el proyecto está enmarcado en la construcción de un ecógrafo ultra-portátil para examinación rutinaria de bajo costo; se busca así la concepción de un equipo de tamaño muy reducido con resoluciones de calidad media, que permitan el pre-diagnóstico rápido de un paciente en casi cualquier lugar. Es por esto que el producto estará enfocado a médicos con conocimientos básicos de imagenología.

Dadas todas las partes y la magnitud que involucra el cálculo, diseño y construcción de un equipo médico, el trabajo se desarrolla en el contexto de un grupo multidisciplinario de ingenieros, abarcando así cada uno de los módulos que conforman el conjunto funcional.

# Capítulo 3

## Diseño e implementación de sistemas.

En este capítulo se describe el diseño e implementación de los sistemas de pulsación, multiplexión y topologías de recepción para la construcción de un ecógrafo ultra-portátil.

Se mostrarán las consideraciones, diseños, simulaciones e implementación de la electrónica y el software desarrollado para conseguir los resultados

#### 3.1 Diseño e implementación de sistema de pulsación Pulser v.1.0

Para el diseño de la primera versión de la plataforma de pulsación, se utiliza directamente un esquema *push-pull* sencillo funcional. A continuación se expone la constitución de cada bloque.

#### 3.1.1 Drivers de corriente para MOSFETs

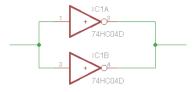

Para una primera aproximación se propone la utilización de compuertas lógicas en paralelo, con el fin de lograr más corriente entrante en las puertas de los MOSFETs. Particularmente se utiliza un inversor séxtuple de tecnología TTL, con corrientes de salida de 50 [mA] por canal¹; luego si se conectan dos en paralelo es posible obtener aproximadamente 100 [mA] de salida. El esquema es sencillo y se muestra en la Figura 19

Figura 19: Configuración de salidas paralelas para obtención de mayor Fan-Out.

Se escoge este circuito como primera aproximación, dada su baja complejidad de implementación. Basta con energizar el circuito integrado, y conectar las entradas digitales para obtener los resultados de entrega de corriente deseados, adicionalmente el encapsulado incorpora 6 puertas lógicas, por lo que es posible energizar 3 compuertas de transistores con cada chip.

-

<sup>&</sup>lt;sup>1</sup> Componente utilizado corresponde a un Hex Inverter 74HC04

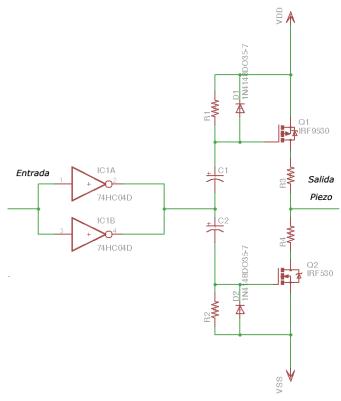

#### 3.1.2 Translación de referencias y pulsadores

Tal como se especificó en los antecedentes de esta memoria, para lograr encender correctamente un transistor MOSFET, se requiere aplicar una tensión en la compuerta suficientemente alta, pero esto es realizable únicamente si se genera un gradiente tal que la corriente fluya hacia la compuerta y no en sentido inverso; en efecto, para un transistor NMOS, la compuerta está referenciada respecto de su terminal de fuente<sup>1</sup>, por lo que la forma de generar el campo eléctrico apropiado es imponiendo una tensión talque V = 0 esté en el nodo correspondiente.

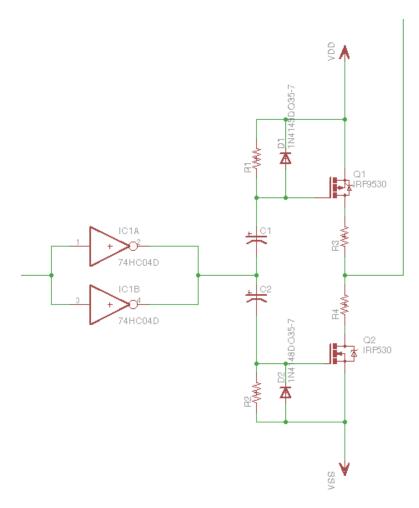

Figura 20: Esquemático del circuito para un pulsador (Versión 1.0)

En este caso la traslación de tensiones se hace a través de dos esquemas:

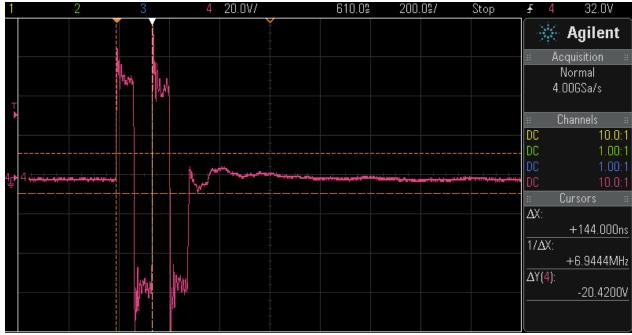

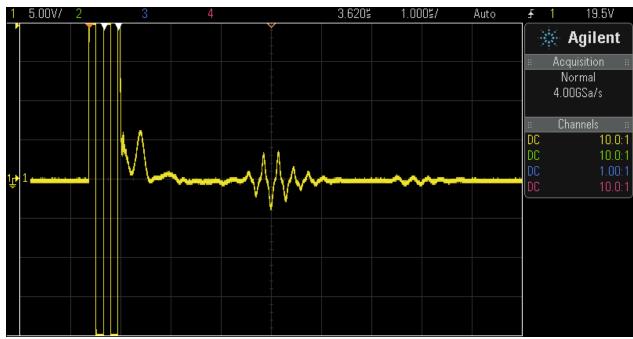

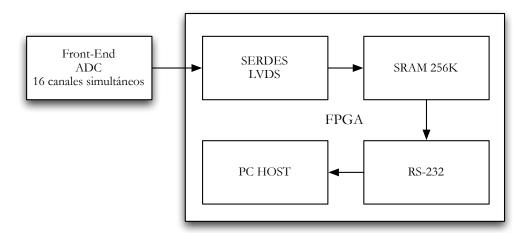

- Condensadores de desacoplamiento, los cuales permiten eliminar la tensión DC presente en la salida de los inversores TTL y volver móvil la señal saliente de estos.