# EVALUACIÓN Y APLICACIÓN DE ESTRATEGIAS PARA CONTROL DE ERRORES EN CANALES SATELITALES MEDIANTE CODIFICACIÓN ALGEBRAICA

# MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA

FELIPE IVÁN TRONCOSO HERNÁNDEZ

PROFESOR GUÍA: MARCOS DÍAZ QUEZADA

MIEMBROS DE LA COMISIÓN: PATRICIO PARADA SALGADO ALEX BECERRA SAAVEDRA

> SANTIAGO DE CHILE AGOSTO 2012

RESUMEN DE LA MEMORIA PARA OPTAR AL TÍTULO DE INGENIERO CIVIL ELECTRICISTA

POR: FELIPE IVÁN TRONCOSO HERNÁNDEZ

FECHA: AGOSTO 2012

PROF. GUÍA: SR. MARCOS DÍAZ QUEZADA

# EVALUACIÓN Y APLICACIÓN DE ESTRATEGIAS PARA CONTROL DE ERRORES EN CANALES SATELITALES MEDIANTE CODIFICACIÓN ALGEBRAICA

En el contexto de las Ciencias Aeroespaciales, surge la necesidad de disponer al alcance de universidades y otros organismos la posibilidad de realizar investigación en el área sin requerir inversiones costosas y planificaciones de largo plazo. Esta idea se concreta actualmente en el lanzamiento de pequeños satélites agrupados bajo el estándar *CubeSat*. El proyecto SUCHAI, del Departamento de Ingeniería Eléctrica, busca poner en órbita el primer satélite de este tipo desarrollado por una Universidad chilena.

Las severas limitaciones de peso, tamaño y recursos de estos satélites impone varios desafíos para mantenerlos funcionales en su órbita. La comunicación con la estación terrestre, desde donde se envían y reciben señales, es crítica para dicho fin. Varios elementos afectan el enlace, como son la alta velocidad de traslación del satélite y el ruido introducido por fenómenos climáticos y la ionosfera. Esto lleva a la necesidad de evaluar mecanismos para minimizar la corrupción en la información transmitida, entre los cuales son de amplia aplicación los esquemas de codificación.

En el contexto del proyecto SUCHAI, este trabajo tiene por objetivos evaluar estrategias de control de errores adecuadas para el entorno descrito, acotando el estudio a los esquemas de codificación algebraica, e implementar aquella que se ajuste mejor a los requisitos impuestos.

La evaluación realizada abarca la simulación de algunas estrategias de codificación, bajo esquemas de modulación en frecuencia y en fase binarios cuyos resultados indican que el código convolucional reduce significativamente los errores en la transmisión. Esto motiva la implementación de un esquema convolucional en un módulo FPGA Spartan-3E de Xilinx, la que se realizó parcialmente en el software ISE.

Con los logros alcanzados, se presentan desafíos de implementación completa y eficiente del código convolucional, realización de pruebas bajo condiciones más realistas a las simuladas, o la evaluación de otros esquemas de codificación y modulación bajo modelos de canal más representativos.

# Agradecimientos

En primer lugar, quiero expresar mi agradecimiento a quienes conforman mi Comisión de este trabajo, los profesores Marcos Díaz, Patricio Parada y el injeniero Alex Becerra, en primer lugar por su actitud de apoyo, disposición, consejo y crítica constantes a lo largo de este proyecto, y en segundo lugar por su incentivo al trabajo bien realizado, cualidad que he intentado aplicar en el desarrollo que expongo, y que me propongo preservar.

En este espíritu debo el reconocimiento al ambiente creado en el laboratorio del proyecto SUCHAI, el que ha influido mucho en mi formación como ingeniero con la capacidad de resolver situaciones prácticas, algo poco enfatizado por la formación teórica de la Escuela. A mis colegas del equipo de Comunicaciones, Sebastián D. y Camilo R., debo desde mi bagaje actual en el software libre hasta las muchas conversaciones sobre cualquier tema, varias veces acompañadas de una cerveza. También a los colegas de programación Tomás O. y Carlos G. con quienes hemos compartido más de una tarde "terraceando". Las experiencias vividas gracias a este proyecto las debo a haberme atrasado en la carrera, por lo que estoy agradecido de dicha circunstancia.

De mi paso por Beaucheff, muchas personas y situaciones influyeron en lo que soy ahora. Doy gracias por todos a quienes conocí en la Pastoral de Injeniería, en la cual participé los dos primeros años de mi carrera: Hernán, Miguel Ángel, Fernando, Claudia, María Teresa, Felipe, Heinz, y muchos otros. A quienes conocí de la Pastoral de la UDP en el memorable viaje a Chiloé, personas a quienes guardo un muy especial aprecio: Belén, Iván, Álvaro, Coté. A mis amigos del colegio que seguimos carrera en la FCFM: Juan, Miguel, Sergio, ha sido increíble lo que hemos cambiado desde el ya lejano 2001 en primero medio, ojalá podamos seguir apreciando nuestro crecimiento en todo ámbito. A mis amigos, integrantes y ex-integrantes de banda: Pablo, Charles, Nano, Marcel, Pailo, sin ustedes no podría haber florecido mi pasión inquieta por la música, y tengo la certeza de que nos hemos enriquecido muchísimo mutuamente.

Finalmente, pero no menos importante, agradezco a mis padres por el apoyo silencioso e incondicional a lo largo de mis años de estudio, y a P., cuyo soporte emocional, amor y amistad no soy capaz de dimensionar.

# Índice general

| 1. | Intr | oducci  | ón                                 | 7  |

|----|------|---------|------------------------------------|----|

|    | 1.1. | Motiva  | ación                              | 7  |

|    | 1.2. | Objeti  | vo General y Alcances              | 8  |

|    | 1.3. | Objeti  | vos Específicos                    | 8  |

|    | 1.4. | Estruc  | tura de la memoria                 | 9  |

| 2. | Asp  | ectos ' | Γeóricos                           | 10 |

|    | 2.1. | Eleme   | ntos de canales de comunicaciones  | 10 |

|    |      | 2.1.1.  | Sistema de comunicaciones          | 10 |

|    |      | 2.1.2.  | Canales discretos                  | 10 |

|    |      | 2.1.3.  | Canales sin memoria                | 11 |

|    |      | 2.1.4.  | Modelos de canal                   | 12 |

|    |      | 2.1.5.  | Capacidad de canal                 | 14 |

|    | 2.2. | Modul   | ación digital                      | 14 |

|    |      | 2.2.1.  | Modulación en banda-base           | 14 |

|    |      | 2.2.2.  | Modulación en pasa-banda           | 16 |

|    | 2.3. | Indica  | dores de desempeño                 | 19 |

|    |      | 2.3.1.  | Energía-bit por densidad espectral | 19 |

|    |      | 2.3.2.  | Probabilidad de error de símbolos  | 20 |

|    |      | 2.3.3.  | Tasa de errores de símbolos        | 21 |

|    |      | 2.3.4.  | Ganancia de código                 | 22 |

|    | 2.4. | Comin   | nicaciones satelitales             | 22 |

| 4. | _    |         | ficaciones de diseño                       | 56 |

|----|------|---------|--------------------------------------------|----|

| 1  | Imp  | lomont  | tación en FPGA                             | 56 |

|    | 3.2. | Conclu  | ısión                                      | 54 |

|    |      | 3.1.11. | Discusión comparativa entre codificaciones | 50 |

|    |      | 3.1.10. | Comparación entre esquemas                 | 49 |

|    |      | 3.1.9.  | Discusión codificación convolucional       | 48 |

|    |      | 3.1.8.  | Simulación codificación convolucional      | 47 |

|    |      | 3.1.7.  | Discusión codificación Reed-Solomon        | 45 |

|    |      | 3.1.6.  | Simulación codificación Reed-Solomon       | 44 |

|    |      | 3.1.5.  | Discusión codificación BCH                 | 42 |

|    |      | 3.1.4.  | Simulación codificación BCH                | 41 |

|    |      | 3.1.3.  | Discusión de caso sin codificación         | 41 |

|    |      | 3.1.2.  | Simulación sin codificación                | 40 |

|    |      | 3.1.1.  | Planteamientos previos                     | 38 |

|    |      |         | ciones canal binario simétrico             | 38 |

| 3. | Sim  | ulacior | nes computacionales                        | 38 |

|    |      | 2.7.2.  | Esquemas de codificación en FPGAs          | 37 |

|    |      | 2.7.1.  | Codificación en canales satelitales        | 36 |

|    | 2.7. | Estado  | del arte                                   | 36 |

|    |      | 2.6.1.  | Field Programmable Gates Array             | 34 |

|    | 2.6. | Diseño  | de hardware digital                        | 34 |

|    |      | 2.5.3.  | Esquemas de codificación más conocidos     | 31 |

|    |      | 2.5.2.  | Códigos lineales de bloques                | 26 |

|    |      | 2.5.1.  | Esquemas de control de errores             | 25 |

|    | 2.5. | Codific | cación para control de errores             | 25 |

|    |      | 2.4.2.  | Descripción de enlaces de baja órbita      | 24 |

|    |      | 2.4.1.  | Descripción general                        | 22 |

|           |        | 4.1.1.  | Codificador convolucional              | 56  |

|-----------|--------|---------|----------------------------------------|-----|

|           |        | 4.1.2.  | Decodificador convolucional            | 57  |

|           | 4.2.   | Implem  | mentación                              | 59  |

|           |        | 4.2.1.  | Codificador convolucional              | 59  |

|           |        | 4.2.2.  | Decodificador convolucional            | 60  |

|           |        | 4.2.3.  | Revisión                               | 62  |

| <b>5.</b> | Con    | clusion | nes                                    | 63  |

|           | 5.1.   | Conclu  | usiones generales                      | 63  |

|           | 5.2.   | Trabaj  | jos Futuros                            | 65  |

| Re        | eferei | ncias   |                                        | 69  |

| Α.        | Dist   | ribuci  | ones de tasas de error en codificación | ]   |

|           | A.1.   | Distrib | bución de BER código BCH               | I   |

|           | A.2.   | Distrib | bución de BER código Reed-Solomon      | III |

|           | A.3.   | Distrib | bución de BER código convolucional     | IV  |

|           | A.4.   | Aspect  | tos de distribuciones observadas       | V   |

# Índice de figuras

| 2.1.  | Canal de comunicaciones                                                                                                                                                                                                                 | 11 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2.  | Canal binario simétrico                                                                                                                                                                                                                 | 12 |

| 2.3.  | Canal AWGN con entrada discretizada                                                                                                                                                                                                     | 13 |

| 2.4.  | Representación discretizada del canal AWGN                                                                                                                                                                                              | 13 |

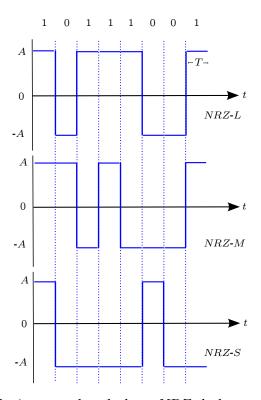

| 2.5.  | Modulaciones en banda-base NRZ de la secuencia 10111001                                                                                                                                                                                 | 15 |

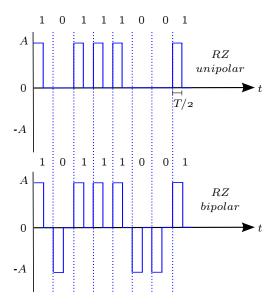

| 2.6.  | Modulaciones en banda-base RZ de la secuencia 10111001                                                                                                                                                                                  | 16 |

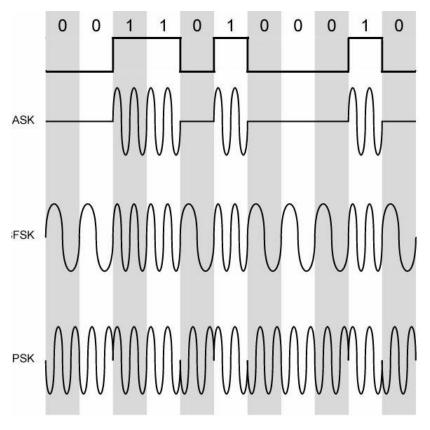

| 2.7.  | Modulaciones básicas pasa-banda                                                                                                                                                                                                         | 17 |

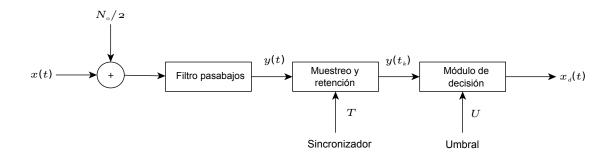

| 2.8.  | Demodulador de símbolos binarios                                                                                                                                                                                                        | 20 |

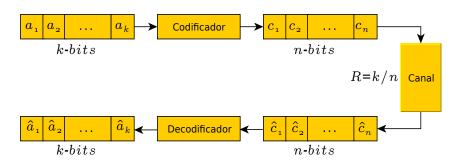

| 2.9.  | Codificación de bloques.                                                                                                                                                                                                                | 27 |

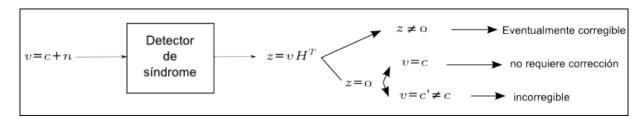

| 2.10. | Detección de síndrome en el decodificador                                                                                                                                                                                               | 30 |

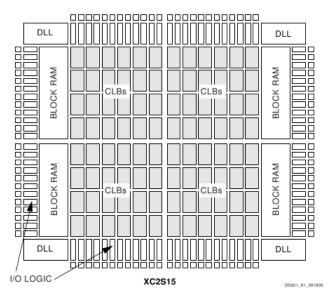

| 2.11. | Bloques funcionales de FPGA Xilinx                                                                                                                                                                                                      | 35 |

| 2.12. | Tarjeta Spartan 3E                                                                                                                                                                                                                      | 35 |

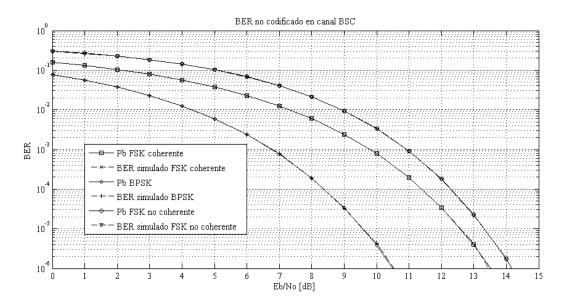

| 3.1.  | BER sin codificación, casos teórico y simulación en canal BSC, para modulación en BPSK, BFSK demodulado en forma coherente y no coherente.                                                                                              | 40 |

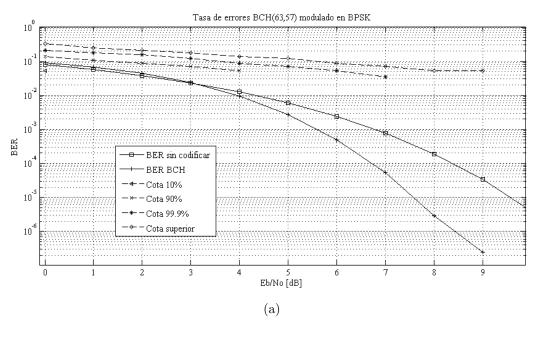

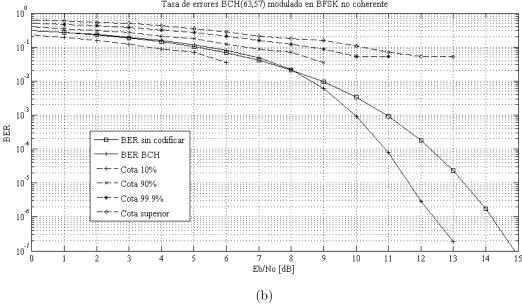

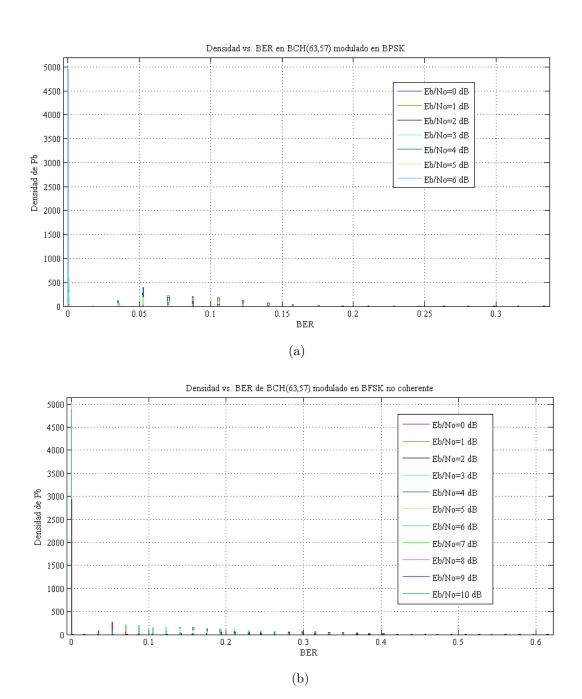

| 3.2.  | Desempeño codificador BCH(63,57) en canal binario simétrico. (a) Modulación BPSK, (b) Modulación BFSK. Nota: el gráfico (a) se ha desplazado levemente a la derecha para apreciar el único valor no nulo en la cota de 10 % (BER=0.0526 |    |

|       | para $E_b/N_0=0$ [dB])                                                                                                                                                                                                                  | 42 |

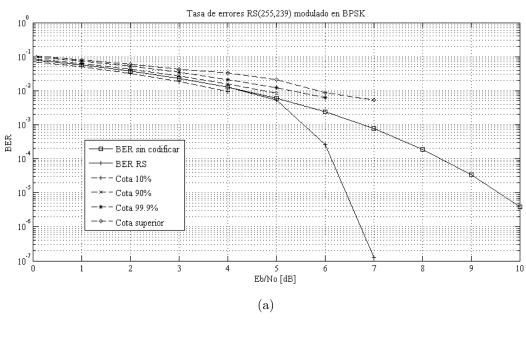

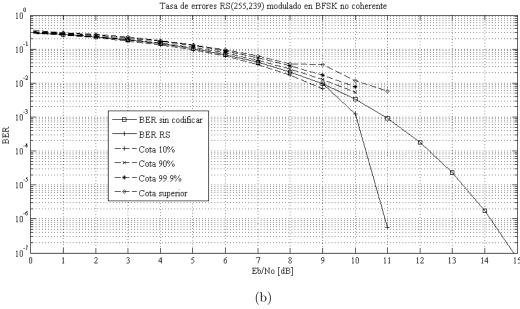

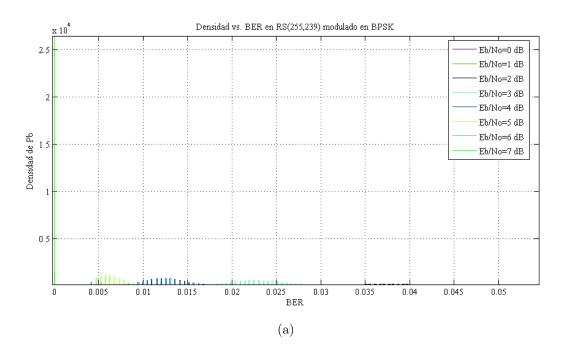

| 3.3.  | Desempeño codificador RS(255,239) en canal binario simétrico.(a) Modulación BPSK, (b) Modulación BFSK                                                                                                                                   | 45 |

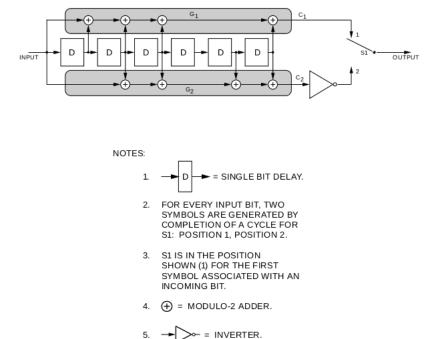

| 3.4.  | Diagrama del codificador convolucional (171,133). Figura extraída de [18]                                                                                                                                                               | 47 |

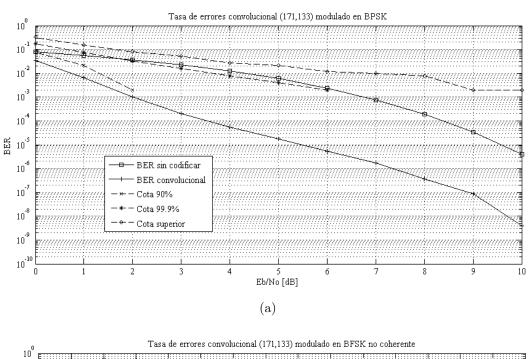

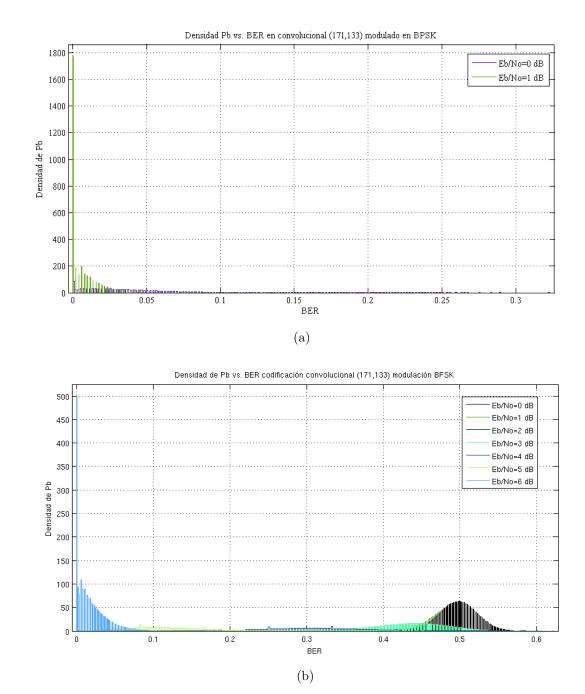

| 3.5.  | Desempeño codificador convolucional (171,133) en canal binario simétrico. (a) Modulación BPSK (b) Modulación BFSK                                                                                                                       | 48 |

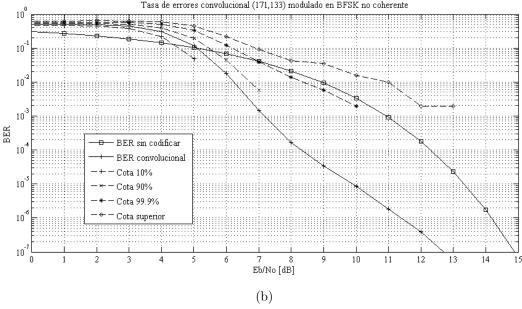

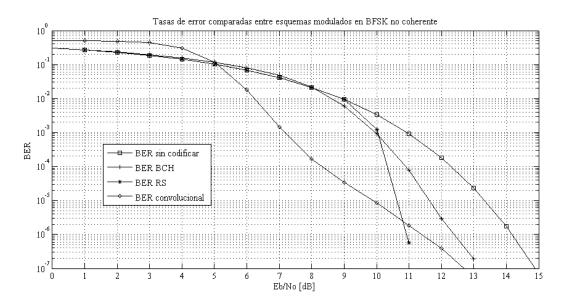

| 3.6. | Desempeño de códigos BCH(63,57), RS(255,239) y Convolucional(171,133) en canal BSC con modulación BPSK                         | 50  |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.7. | Desempeño de códigos BCH(63,57), RS(255,239) y Convolucional(171,133) en canal BSC, modulación BFSK con detección no coherente | 50  |

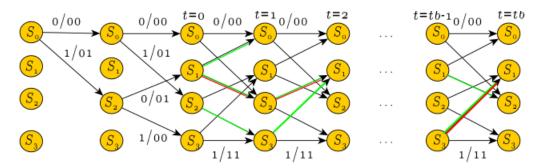

| 4.1. | Enmallado de decodificación para un codificador con $K=2$ unidades de memoria                                                  | 57  |

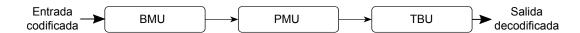

| 4.2. | Unidades principales del decodificador con algoritmo de Viterbi                                                                | 58  |

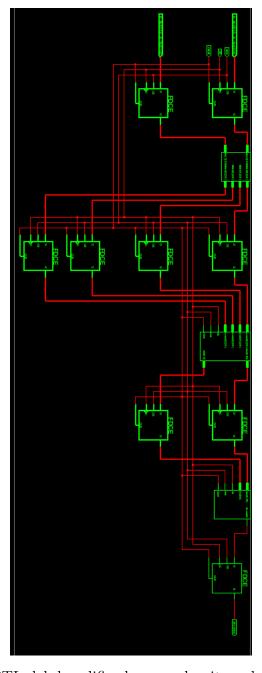

| 4.3. | Esquemático RTL de codificador convolucional (2,1,7) realizado en ISE                                                          | 59  |

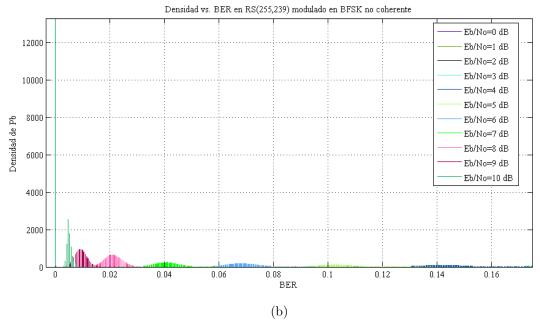

| 4.4. | Utilización de recursos en FPGA para decodificador Viterbi, generado en ISE.                                                   | 60  |

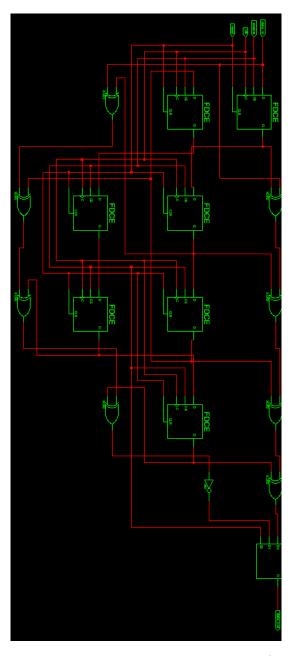

| 4.5. | Esquemático RTL del decodificador con algoritmo de Viterbi, generado en ISE.                                                   | 61  |

| 4.6. | Utilización de recursos en FPGA para decodificador Viterbi, generado en ISE.                                                   | 62  |

| A.1. | Distribución de BER en código BCH(63,57) en canal binario simétrico. (a) Modulación BPSK, (b) Modulación BFSK                  | IJ  |

| A.2. | Distribución de BER en código $RS(255,239)$ en canal binario simétrico. (a) Modulación BPSK, (b) Modulación BFSK               | III |

| A.3. | Distribución de BER en código convolucional(171,133) en canal binario simétrico. (a) Modulación BPSK, (b) Modulación BFSK      | ΙV  |

# Índice de tablas

| 2.1. | Operaciones en $GF(2)$                                                                                               | 28 |

|------|----------------------------------------------------------------------------------------------------------------------|----|

| 2.2. | Capacidad de corrección $t$ de códigos $\mathrm{BCH}(n,k)$ en función de $R=k/n$ con $n=63$ . Tabla extraída de [42] | 32 |

| 3.1. | Ganancias de modulación BPSK respecto a BFSK no coherente, para tasas de error de $10^{-3}$ , $10^{-4}$ y $10^{-5}$  | 41 |

| 3.2. | Comparación de potencias requeridas para esquemas de codificación con modulación BPSK, en [dB]                       | 51 |

| 3.3. | Comparación de potencias requeridas para esquemas de codificación con modulación BFSK, en [dB]                       | 51 |

| 3.4. | Ganancias de código con modulación BPSK, en [dB]                                                                     | 52 |

| 3.5. | Ganancias de código con modulación BFSK, en [dB]                                                                     | 52 |

| 3.6. | Tasas de código para esquemas de codificación                                                                        | 54 |

# Capítulo 1

# Introducción

### 1.1. Motivación

Desde principios de la década actual se ha extendido ampliamente la creación de satélites de baja órbita, a nivel de investigación y aplicación académica, que permiten disponer al alcance de estudiantes de variados niveles y académicos nuevos desafíos tecnológicos, y al mismo tiempo fomentar la investigación de una amplia diversidad de fenómenos de manera innovadora. Este desarrollo se inició en los laboratorios de la Universidad Politécnica de California (CalPoly) y de la Universidad de Stanford en 1999; hoy se ha ampliado a un número creciente de Universidades y organismos tanto civiles como gubernamentales.

Los pequeños satélites lo conforman aquellos de tamaño y peso reducidos, usualmente bajo los 500 [kg], con combustible incluido [55]. Este grupo se divide en varios subgrupos de acuerdo a su tamaño, peso, propósito u otros criterios, y presenta ventajas en relación a costos, rapidez de desarrollo, objetivos acotados y multiplicidad de aplicaciones. Dentro de esta categoría, destaca el estándar *CubeSat*, originado en las universidades previamente mencionadas, cuyas características son su forma cúbica, de 10 [cm] de longitud, y un peso máximo de 1.3 [kg] constituido por la estructura y componentes del satélite. Este estándar es el empleado con frecuencia por las entidades mencionadas en el párrafo anterior.

En el año 2010, el Departamento de Ingeniería Eléctrica (DIE) de la Universidad de Chile se unió a este desafío y actualmente el profesor Marcos Díaz (DIE), en conjunto con otros dos académicos del DIMEC y del DFI, dirigen este proyecto cuyo lanzamiento se espera para fines de 2012. Este proyecto se ha denominado SUCHAI (Satellite of University of Chile for Aerospace Investigation) y además del lanzamiento mismo del satélite, busca ser el comienzo de una nueva área de investigación aeroespacial dentro del Departamento de Ingeniería Eléctrica.

Dentro del funcionamiento de un satélite es crucial asegurar que los datos enviados o recibidos por la unidad de comunicaciones sean confiables, es decir que los errores producidos en el enlace sean reducidos a una cantidad mínima. En comunicaciones digitales, una de las maneras de resolver esta situación es utilizando codificación de canal, la que mediante

diversos enfoques puede reducir la tasa de errores en la transmisión. El estudio y aplicación de un mecanismo de codificación es el enfoque del presente trabajo.

# 1.2. Objetivo General y Alcances

En el marco del proyecto satelital de SUCHAI, y de la proyección de construir un dispositivo de comunicaciones en el Departamento de Ingeniería Eléctrica, el objetivo general de este trabajo consiste en la investigación e implementación de un prototipo de codificador y decodificador que permita detectar y corregir los errores producidos en un canal satelital de baja órbita, situado entre 200 y 800 kilómetros de altitud. El prototipo es realizado utilizando módulos de desarrollo electrónicos basados en FPGAs disponibles en el Departamento de Ingeniería Eléctrica (Electrotecnologías). Tras una primera etapa de simulaciones computacionales, que permiten seleccionar el esquema de codificación a aplicar, éste se implementa en FPGA. Finalizado este trabajo, quedarán a disposición del laboratorio del proyecto SUCHAI los códigos computacionales de simulación e implementación, de manera que si eventualmente se construye el dispositivo de comunicaciones, pueda ser añadido un esquema de codificación y decodificación, y del mismo modo en la estación terrena.

Cabe señalar que, establecido el objetivo general, queda excluido el diseño de una placa o bloque para ser incluido en el lanzamiento, pues dicha labor además debería considerar la inclusión de etapas de modulación, amplificación, intercambio de datos con el procesador satelital, conexión a la antena y adecuar dicha placa a las restricciones del satélite.

# 1.3. Objetivos Específicos

Los objetivos específicos permiten enlistar las labores fundamentales a cumplir para concretar el objetivo principal de este trabajo, a saber:

- Revisión bibliográfica del estado del arte y análisis de los principales códigos. Para esto se realiza un estudio teórico, plasmado en el Capítulo 2, donde se resumen las características de los códigos más usuales, además de conceptos adicionales necesarios para su comprensión.

- Simulaciones computacionales de canales con modulación pasabanda, codificados y no-codificados, para comparar sus comportamientos y seleccionar el esquema de codificación con mejor desempeño.

- Decisión del esquema de codificación y decodificación a implementar. Esto requiere conocer las ventajas y limitaciones de los algoritmos tanto para codificar como para decodificar, pues puede existir un trade-off entre las mejoras propias del código y su complejidad de implementación.

• Implementación del prototipo. Esto requiere contar tanto con el hardware adecuado (tarjeta de desarrollo en FPGA, computador adecuado) y el software necesario (suite de Xilinx ®ISE). Bajo este objetivo se implementan el codificador y decodificador vía lenguaje descriptivo de hardware (HDL) o esquemáticos digitales, para ser embebidos en la arquitectura de la FPGA.

### 1.4. Estructura de la memoria

La estructura utilizada en este documento para exponer el trabajo realizado es la siguiente:

- Capítulo 1. Introducción: Corresponde a la descripción del tema, la motivación de éste y los alcances y objetivos del trabajo realizado.

- Capítulo 2. Aspectos Teóricos: Corresponde a la revisión bibliográfica o antecedentes. En este capítulo se explican los conceptos necesarios para la comprensión y contextualización del trabajo.

- Capítulo 3. Simulaciones computacionales: Se analizan mediante simulaciones los diversos esquemas de codificación; de este modo se decide con criterios cuantitativos el esquema de codificación a implementar.

- Capítulo 4. Implementación en FPGA: Se realiza la implementación en hardware del esquema utilizado, tanto para el codificador como el decodificador.

- Capítulo 5. Conclusiones: Se concluye con los resultados obtenidos, discutiendo la cobertura de los objetivos y el alcance del trabajo. Se exponen además los posibles aportes futuros, tales como la implementación del hardware, sea ésta para uso académico como prototipo ó para ser incluido en vehículos aeroespaciales.

# Capítulo 2

# Aspectos Teóricos

#### 2.1. Elementos de canales de comunicaciones

#### 2.1.1. Sistema de comunicaciones

Un sistema de comunicaciones se constituye de tres elementos principales: el transmisor, desde donde se envía la información deseada; el receptor, donde es recibida, y el canal, medio físico entre el transmisor y el receptor. Es posible transmitir información mediante una señal que varía de forma continua, constituyendo una señal analógica. De otro modo, los datos pueden ser transformados en un conjunto de valores discretos, en lo que se denomina una señal digital. En cualquier caso, la información transmitida sufre degradación por diversas fuentes físicas de ruido en el canal y en el receptor.

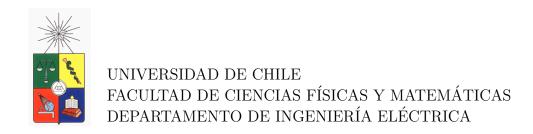

En un sistema de comunicaciones cuyas señales son digitales (Figura 2.1), el transmisor y el receptor cuentan con módulos que procesan la señal para ser enviada a través de un medio físico. Un **codificador** detecta y/o corrige los errores producidos en el canal modificando la trama de datos, por lo general añadiendo bits de redundancia. En la etapa posterior, un **modulador** transforma el mensaje digital en bits a señales analógicas mediante algún esquema de modulación determinado. De manera similar, en el receptor se tendrá un **demodulador** que transforma la señal recibida en bits, y un **decodificador** que utiliza la redundancia o modificación introducida para detectar y/o corregir los errores que el canal introdujo.

#### 2.1.2. Canales discretos

Un canal discreto corresponde a la abstracción de un canal de transmisión físico, incluyendo las etapas de modulación y demodulación; por ello está caracterizado por entradas y salidas que toman una cantidad finita de valores. En casos prácticos como un sistema

Figura 2.1: Canal de comunicaciones

satelital, el canal produce formas de onda continuas en el tiempo en su salida<sup>1</sup>, lo que lo constituye como canal analógico. Esta forma de onda puede tener cualquier amplitud real, limitada por la potencia máxima del transmisor o del ruido introducido por el canal, y su espectro en frecuencia es limitado por el ancho de banda del equipo receptor. Por medio de las hipótesis descritas en la Definición 2.1.2, el canal mencionado puede ser tratado como discreto.

En el caso de un canal discreto finito, la cantidad de valores que toman las entradas y salidas son finitas. El conjunto acotado de valores posibles en la entrada se denomina **alfabeto de entrada**. Análogamente, en la salida tomará sus valores en un **alfabeto de salida**. Los elementos de cada alfabeto se denominan **símbolos**. Esto permite definir un canal discreto como la correspondencia entre el alfabeto de entrada y el de salida: si x es un símbolo de entrada, e y el símbolo de salida, el canal asigna el valor y con probabilidad p(y|x) al transmitir x [45, Cap. 9].

#### 2.1.3. Canales sin memoria

En términos generales, la salida de un canal discreto  $y_i$  depende no sólo de la entrada  $x_i$  correspondiente a ese instante, sino que de las entradas anteriores (en el caso de los canales con interferencia inter-simbólica), e incluso de entradas futuras (como en medios de almacenamiento [45, Cap. 9]). En tales casos la dependencia entre los símbolos se denomina memoria. Un canal discreto cuya salida  $y_i$  depende sólo de la entrada respectiva  $x_i$  se dirá sin memoria (DMC). Para este canal se cumple que, para una secuencia de símbolos de entrada  $\mathbf{x}$  y salida  $\mathbf{y}$ , ambas de largo n, la probabilidad conjunta entre  $\mathbf{x}$  e  $\mathbf{y}$  está dada por:

(2.1)

$$p(\mathbf{y}|\mathbf{x}) = \prod_{i=1}^{n} p(y_i|x_i).$$

<sup>&</sup>lt;sup>1</sup>O en la entrada del demodulador.

#### 2.1.4. Modelos de canal

La naturaleza del medio físico puede ser modelada matemáticamente, lo cual da origen a varias familias de canal que se emplean en el área de comunicaciones. Los modelos principales que guardan relación con este trabajo son los siguientes:

**Definición 2.1.1** Un canal binario simétrico (BSC, Figura 2.2) es aquel canal DMC donde el alfabeto de entrada **I** y el alfabeto de salida **O** constan de dos símbolos llamados bits, denotados por '0' y '1', donde la probabilidad de que cualquiera de dichos símbolos sea transmitido correctamente es 1-p, y complementariamente, la probabilidad de que un símbolo '0' cambie a '1' o viceversa es p [11, Cap. 1].

Figura 2.2: Canal binario simétrico

Definición 2.1.2 Un canal de ruido blanco gaussiano aditivo (AWGN) continuo es un modelo de canal aleatorio cuya salida es un proceso real aleatorio. En términos matemáticos la salida Y(t) se define como:

$$(2.2) Y(t) = X(t) + N(t)$$

donde X(t) es la forma de onda en la entrada vista como proceso aleatorio real, y N(t) es un proceso real de ruido gaussiano blanco con densidad de potencia de ruido  $N_0$ , independiente de X(t).

La señal X(t) tiene potencia con media P; además es acotada en el canal de banda B, siendo éste el intervalo de frecuencias no-negativas con **ancho de banda** W, medido en [Hz]. Dicho canal de banda es **banda-base** si B = [0, W], **pasa-banda** si  $B = [W_0, W]$ ,  $W > W_0 > 0$ , y **pasa-alto** si  $B = [W, \infty[$ . Los parámetros que permiten caracterizar un canal AWGN continuo son su ancho de banda W y su **razón señal-a-ruido** SNR. Este último parámetro está dado por:

$$(2.3) SNR = \frac{P}{N_0 W}$$

donde  $N_0W$  es la potencia de ruido total en la banda B, y P la potencia de la señal modulada.

Dado un ancho de banda W, el teorema del muestreo establece que la señal continua se debe muestrear a una tasa de 2W para ser reconstruida sin pérdida de información; además,

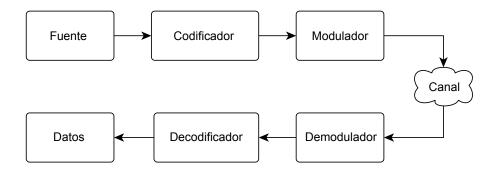

el teorema de irrelevancia permite asegurar la detección de X(t) a partir del muestreo de Y(t) desde un canal con ruido AWGN [20]. Dadas las hipótesis del modelo continuo, los procesos gaussianos X(t) y N(t) pueden ser reformulados como secuencias discretas  $\mathbf{X}$  y  $\mathbf{N}$  respectivamente, y por tanto el modelo mismo puede ser considerado como de tiempo discreto [20, Cap. 2]. Al discretizar el canal AWGN, es posible representar la entrada como un alfabeto discreto  $\mathcal{X} \in \{a_1, a_2, ..., a_Q\}$  cuya salida  $\mathcal{Y} \in (-\infty, \infty)$  es una probabilidad dada por [57, Cap. 1]:

(2.4)

$$p(y|a_k) = \frac{1}{\sqrt{2\pi\sigma^2}} e^{-(y-a_k)^2/2\sigma^2} \quad \text{para todo } y \in \mathbf{Y}$$

donde k = 1, 2, ..., Q. La Figura 2.3 ilustra este modelo.

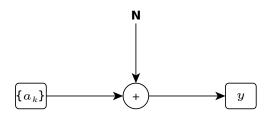

Figura 2.3: Canal AWGN con entrada discretizada.

La discretización de las secuencias de entrada y de ruido AWGN no implica que las salidas tomen valores discretos, como se observa en la Ecuación 2.4. Sin embargo, como se verá posteriormente, los esquemas de codificación se implementan en la práctica mediante circuitos digitales, por lo que es conveniente buscar una representación discretizada completa del canal AWGN, incluyendo sus salidas. Mediante la cuantización implementada en el dispositivo demodulador, la salida continua de este último es transformada a secuencias digitales. Dependiendo de la cantidad de secuencias de salida posibles (estados), la relación entre las secuencias discretas entrantes al canal y las de salida del demodulador definen el modelo de canal que equivale a una representación digital del canal AWGN [57, Cap. 2]. La Figura 2.4 esquematiza el canal equivalente, discretizado del modelo AWGN. Esta reformulación permite considerar el canal AWGN, el modulador y el demodulador como un único ente, cuya entrada proviene del codificador de canal y cuya salida accede al decodificador de canal. En este trabajo se considera que la relación entre las entradas y salidas conforman un canal DMC.

Figura 2.4: Representación discretizada del canal AWGN.

#### 2.1.5. Capacidad de canal

Todo canal de transmisión introduce errores a la señal que se envía a través de él. Las características particulares de dicho canal lo hacen más o menos confiable para transmitir información. En una comunicación confiable, es posible reducir o limitar la cantidad de errores generados.

**Definición 2.1.3** La capacidad del canal C corresponde al límite de símbolos por unidad de tiempo que pueden ser transmitidos de forma confiable a través de dicho canal.

El concepto de capacidad de canal acota la tasa de transmisión que posibilita una comunicación confiable. En 1948, C. Shannon establece teóricamente la manera de mejorar la confiabilidad de un canal, relacionándola a la tasa de transmisión R empleada en un sistema de comunicaciones:

**Teorema 2.1.1** Si la tasa de transmisión R es menor a la capacidad de canal C, entonces es posible diseñar un esquema de codificación de canal, cuya probabilidad de error en los símbolos de salida sea tan pequeña como se desee [51].

De esta manera, si la tasa de transmisión R supera la capacidad del canal, no será posible limitar mediante codificación la tasa de errores.

En un canal binario simétrico, dada la probabilidad p de error, la capacidad es [44, Cap. 7]:

(2.5)

$$C_{BSC} = 1 + p \log_2(p) + (1 - p) \log_2(1 - p) \quad [bps].$$

En un canal continuo AWGN, la capacidad está dada por [45, Cap. 9]:

(2.6)

$$C = W \cdot log_2(1 + SNR) \quad [bps].$$

## 2.2. Modulación digital

La modulación digital es un proceso que transforma una secuencia de símbolos digitales en una señal apta para ser transmitida en un medio físico analógico. Para distancias cortas, se usa modulación en banda-base, llamada a veces codificación de línea (line coding) [64, Cap. 2]. Para distancias largas, y transmisión inalámbrica en particular, se usa la modulación pasabanda, también conocida como modulación por portadora (carrier modulation) [64, Cap. 2]. Ambos esquemas se exponen a continuación.

#### 2.2.1. Modulación en banda-base

Se entiende la modulación en banda-base como la representación de secuencias digitales mediante formas de onda adecuadas para la transmisión en canal de banda-base B = [0, W]

para alguna frecuencia W>0, sin realizar transformación en frecuencia. Existe una gran variedad de esquemas de modulación en banda-base, desarrollados para responder a propiedades deseadas tales como eficiencia en potencia y ancho de banda, o sincronización adecuada [64, Cap. 2].

En la Figura 2.5 se agrupan tres esquemas correspondientes a modulación NRZ ( $Non-Return\ to\ Zero$ ). En el esquema NRZ-L, se emplean dos niveles de amplitud  $A\ y\ -A$  para identificar los dígitos binarios '1' y '0', respectivamente. En el esquema NRZ-M, un cambio de nivel de  $A\ a\ -A$  o viceversa es usado para señalizar un '1', mientras que el '0' se representa sin realizar transición. El esquema es similar en NRZ-S, pero el cambio de nivel señaliza el bit '0'. Estas dos últimas formas de modulación son parte de las llamadas  $codificaciones\ diferenciales$ . En cuanto a aplicaciones, NRZ-L es de uso extensivo en lógica digital y NRZ-M se emplea principalmente en grabación en cinta magnética. La limitación principal de estos esquemas es la dificultad de recuperar los ciclos de reloj ( $clock\ recovery$ ) cuando se transmiten secuencias largas de un mismo estado '0' ó '1'. Debido a esto, el uso de esquemas NRZ se restringe a redes de corto alcance, como es el caso de las redes de área local [64, Cap. 2].

Figura 2.5: Modulaciones en banda-base NRZ de la secuencia 10111001.

La dificultad de recuperar los ciclos de reloj en el caso de NRZ puede ser resuelta incluyendo más transiciones en la forma de onda. Esto se realiza empleando la denominada modulación RZ (*Return to Zero*). En su versión unipolar, el bit '1' se representa como un pulso de medio periodo de duración, y el '0' como el nivel cero en toda su duración. En el modo bipolar, tanto el '1' y el '0' se representan con niveles de amplitud no-nulos y de signo distinto, con medio periodo de duración, mientras la segunda mitad del periodo está en

nivel nulo. Este formato asegura dos transiciones por bit, mejorando las características de recuperación de ciclos de reloj, con la contraparte de que requiere el doble de ancho de banda que en el caso de NRZ [64, Cap. 2]. Este esquema se representa en la Figura 2.6.

Figura 2.6: Modulaciones en banda-base RZ de la secuencia 10111001.

## 2.2.2. Modulación en pasa-banda

#### Esquemas básicos

En la modulación pasa-banda, una secuencia de símbolos digitales modifican los parámetros de una señal sinusoidal de alta frecuencia, denominada *portadora*. Dado que dicha señal tiene amplitud, frecuencia y fase, son estos parámetros los que pueden modificarse para modular la señal. De este modo, se originan tres esquemas básicos de modulación pasa-banda (Figura 2.7):

- 1. Modulación por desplazamiento de amplitud ASK (Amplitude Shift Keying), en la que cada símbolo '1' genera una ráfaga de la señal portadora de amplitud A, y un '0' genera una señal de amplitud  $B \neq A$ . Si una de ambas amplitudes es 0, el esquema se denomina OOK (On-Off Keying).

- 2. Modulación por desplazamiento de frecuencia BFSK (Binary Frequency Shift Keying), donde el símbolo '1' se representa por una ráfaga de una frecuencia  $f_1$  y el símbolo '0' por una ráfaga de frecuencia  $f_2 \neq f_1$ . Ambas frecuencias se calculan a partir de una frecuencia nominal  $f_c$ , dependiendo de las propiedades deseadas para este esquema (ver sección 2.2.2).

- 3. Modulación por desplazamiento de fase BPSK (Binary Phase Shift Keying), en la que el símbolo '1' se modula con una ráfaga con fase  $\theta$ ° y el '0' con una ráfaga con desfase de

$(\theta-180)^{\circ}$ . Esta diferencia en fase minimiza la probabilidad de error de demodulación (ver Sección 2.3.2), aunque en un esquema PSK general puede tomar cualquier valor en el rango  $[0^{\circ}, 360^{\circ}]$ .

A partir de estos modos básicos de modulación pasa-banda, se han desarrollado otros esquemas con características particulares en fase, frecuencia y amplitud, con desempeños resultantes diversos en cuanto a eficiencia en potencia, eficiencia en ancho de banda y complejidad de implementación [64, Cap. 1].

Figura 2.7: Modulaciones básicas pasa-banda.

Cabe señalar que la modulación de los símbolos se realiza, para cada esquema visto, de acuerdo al formato en que se representan en banda- base. En tal caso, si los símbolos son previamente modulados con codificación diferencial (en banda-base), la forma de onda modulada en pasabanda será distinta que si la codificación es no-diferencial, como en el caso de NRZ-L. Esto es de importancia al considerar características tales como eficiencia de potencia, ancho de banda y complejidad de implementación en el diseño de moduladores y demoduladores.

#### Características de modulaciones BFSK y BPSK

En modulación BFSK, dos aspectos inciden en su comportamiento. El primero es la coherencia, definida como la igualdad de las fases de las dos frecuencias seleccionadas en torno a una frecuencia nominal  $f_c$ ; si tales fases son iguales, el esquema se dice coherente, y en caso contrario se denomina no coherente. En la modulación coherente, las transiciones de bits se realizan preservando la fase, y por lo tanto la forma de onda mantiene su continuidad en el tiempo.

El segundo aspecto es la ortogonalidad de frecuencias; en un esquema coherente, las dos frecuencias  $f_1$  y  $f_2$  son ortogonales si ambas son múltiplos de 1/4T, donde T es el periodo de 1-bit, y además la separación entre ambas debe ser  $2\Delta f = f_1 - f_2 = k/2T$ , con k entero. En un esquema BFSK no coherente, las frecuencias ortogonales son múltiplos de 1/2T y la separación entre ellas es múltiplo de 1/T. Esto implica que se duplica el ancho de banda requerido para una transmisión no-coherente, considerando la misma tasa de datos  $R_b = 1/T$ . Un esquema FSK modulado en forma coherente, con frecuencias ortogonales con separación de frecuencias igual a 1/T se denomina FSK de Sunde y corresponde a un caso especial de las modulaciones CPFSK ( $continuous\ phase\ FSK$ ).

Finalmente, es posible demodular una señal coherente tanto de forma coherente como no-coherente, lo que depende de si se recuperan las fases de las frecuencias recibidas; una señal modulada de forma no-coherente, sin embargo, sólo puede ser demodulada de forma no-coherente. Esta última demodulación es la más usual debido a la dificultad de construir un recuperador de portadora que obtenga las fases [64, Cap. 3].

Para caracterizar el comportamiento de la modulación BPSK se utilizan conceptos distintos. En este esquema se modula el dígito binario '1' con una señal sinusoidal  $s_1(t)$  y el símbolo binario '0' con una señal  $s_2(t) = -s_1(t)$ ; dichas señales se denominan antipodales. La diferencia en signo de las señales  $s_1(t)$  y  $s_2(t)$  tiene por consecuencia un desfase de 180° entre ellas. La demodulación de una señal BPSK es coherente cuando se requiere recuperar la fase de la señal recibida, y sincronizarla con la señal de referencia del correlador respectivo; además debe satisfacerse que la frecuencia de la señal,  $f_c$ , sea múltiplo entero de la tasa de datos  $R_b$ . Aún así, esta condición puede relajarse si  $f_c >> R_b$ , con una degradación despreciable en la tasa de errores de demodulación.

Una forma opcional es la dada por la modulación PSK diferencial, denotada por DEBPSK. En este formato, los bits de datos se codifican diferencialmente, y luego se modulan en fase de la forma descrita previamente. Esta codificación previa a la modulación permite emplear un demodulador diferencial, que toma el símbolo previo demodulado como referencia para calcular el símbolo actual, en lugar de requerir una señal de referencia sincronizada en fase y frecuencia. Un esquema con codificación diferencial en el modulador y demodulación diferencial se denomina DPSK <sup>2</sup>. Esta modulación no requiere la mencionada sincronización, pero su implementación es más compleja y el desempeño con respecto a BPSK coherente es

<sup>&</sup>lt;sup>2</sup>El acrónimo DEBPSK alude sólo al formato codificado de modulación. El término DPSK incluye además la demodulación diferencial.

inferior <sup>3</sup>. En cualquiera de estos mecanismos de modulación, los datos binarios ingresan al modulador representados en formato banda-base NRZ [64, Cap. 4].

#### Modulación MSK

El esquema MSK reúne características de modulación en fase, pues adecúa la forma de onda del esquema OQPSK<sup>4</sup>, y se visualiza además como un caso particular de modulación FSK en fase continua (CPFSK) [64, Cap. 5]. Visto de este último modo, MSK corresponde a la mínima separación entre frecuencias que permite generar señales ortogonales coherentes. Es por ello que este esquema es particularmente eficiente en ancho de banda. Existen varias formas de implementar un modulador MSK, basadas en su símil de OQPSK. El demodulador puede construirse en base al de este último esquema, para detectar la señal en forma coherente, o puede realizarse con un esquema de enmallado con algoritmo de Viterbi, puesto que MSK es además un tipo de modulación de fase continua (CPM). La tasa de errores (ver Sección 2.3.2) producidas en el demodulador coherente son idénticas al caso de la modulación BPSK y QPSK. Dado que MSK es una forma de FSK, puede también detectarse de forma nocoherente, con alrededor de 1 [dB] de pérdida de eficiencia en potencia. [64, Cap. 5]. Por las propiedades mencionadas, este esquema conjuga el buen desempeño en errores de BPSK con eficiencia en ancho de banda, y representa una alternativa para la construcción de un módulo de comunicaciones.

# 2.3. Indicadores de desempeño

Para evaluar el funcionamiento de un esquema de comunicaciones o alguna de sus partes, se requieren indicadores que permitan caracterizar su comportamiento y compararlo adecuadamente con otras alternativas. Los señalados a continuación son usuales en el estudio de sistemas de comunicación digital.

## 2.3.1. Energía-bit por densidad espectral

Se menciona en la Definición 2.1.2 la razón señal a ruido SNR, que en conjunto con el ancho de banda W caracterizan completamente un canal AWGN. Una manera similar de describir el efecto del ruido sobre señales discretas es la razón energía-bit por densidad espectral de ruido, denotada  $E_b/N_0$ , y corresponde a la energía portada por cada bit transmitido, en razón a la densidad espectral del ruido del canal. Se tiene que

$$\frac{E_b}{N_0} = \frac{S}{N_0 r_b} \quad [dB]$$

$<sup>^3</sup>$ Para una tasa de errores en demodulación de  $10^{-4}$ , DPSK requiere 0.8 [dB] más de potencia que en BPSK.

$<sup>^4</sup>$ OQPSK corresponde a la modulación en fase de 4 símbolos (QPSK), modificada de tal manera que la diferencia de fase en las señales de salida no supera  $\Delta\theta = 90^\circ$  [46, Ap. D].

donde  $r_b$  es la tasa de símbolos, medida en [bps], y S la potencia de la señal en banda-base portadora de 1 bit, de duración  $T \leq T_b = 1/r_b$  [11]. Es importante notar de la ecuación 2.7 que el nivel de  $E_b/N_0$  depende tanto de la potencia de la portadora, dependiente a su vez de la modulación banda-base usada para representar las secuencias binarias, como de la tasa de símbolos, siendo distinto al caso del SNR que depende de la potencia de la señal y del ancho de banda.

#### 2.3.2. Probabilidad de error de símbolos

Se desprende de las definiciones 2.1.1 y 2.1.2 que al transmitir símbolos en un canal, existe una probabilidad asociada de que dicho canal los modifique, y por lo tanto el demodulador les asignará un valor digital incorrecto. Luego, otra forma de medir el desempeño es considerar los errores cometidos en la demodulación de una señal binaria [5].

En una transmisión de símbolos binarios en un canal AWGN, el demodulador consiste esencialmente de tres etapas: un filtro pasa-bajos, que elimina cierta parte del ruido de entrada, un módulo de muestreo sincronizado de la señal filtrada, y un módulo de decisión de símbolos. En el tercer módulo se decide si el símbolo recibido corresponde a un 1 ó un 0 binario; tal decisión se lleva a cabo comparando el valor de entrada de la señal  $y(t_k)$  con un valor denominado umbral U (ver Figura 2.8), el cual se escoge de modo que los errores cometidos sean equiprobables para ambos símbolos binarios. Este método de selección se conoce como hard decision y es válido sólo en condiciones de ruido gaussiano y con símbolos equiprobables. Si los símbolos no son equiprobables se utilizan otros métodos como máxima probabilidad a-posteriori (MAP) o estimación de máxima verosimilitud (MLE) [5]. En este contexto se establecen sólo las probabilidades de error en demodulación  $P_b$  para señales equiprobables y con energías iguales, en un canal AWGN.

Figura 2.8: Demodulador de símbolos binarios.

La función Q(a), relacionada con las probabilidades de error, se define como la probabilidad de que una variable aleatoria X sea mayor que un valor a bajo una distribución

gaussiana normal  $\mathcal{N}(0,1)$  [5]:

(2.8)

$$Pr\{X > a\} = Q(a) = \frac{1}{\sqrt{2\pi}} \int_a^\infty \exp\left(\frac{-x^2}{2}\right) dx$$

Bajo las condiciones mencionadas, la probabilidad de error  $P_b$  dependerá de la demodulación. Dicha probabilidad también es afectada por la forma de modulación, en particular por la coherencia de fases en FSK y la discontinuidad de la forma de onda en PSK. De este modo, para un esquema PSK binario no diferencial, demodulado coherentemente  $^5$ ,  $P_b$  está dada para cada símbolo binario como [64, Cap. 4]

(2.9)

$$P_{b \text{ (BPSK)}} = Q\left(\sqrt{\frac{2E_b}{N_0}}\right)$$

Para un esquema FSK de Sunde, demodulado en forma coherente, la probabilidad de error es [64, Cap. 3]:

(2.10)

$$P_{b \text{ (BFSK coh.)}} = Q\left(\sqrt{\frac{E_{b}}{N_{0}}}\right)$$

y bajo FSK con demodulación no-coherente y frecuencias ortogonales, dicha probabilidad es [64, Cap. 3]:

(2.11)

$$P_{b \text{ (BFSK no coh.)}} = \frac{1}{2}e^{-E_{b}/2N_{0}}$$

#### 2.3.3. Tasa de errores de símbolos

Un parámetro empírico de importancia es la tasa de errores en el mensaje recibido en comparación con el mensaje enviado. Esta tasa se denota BER ( $bit\ error\ rate$ ). Al recibir una secuencia de largo n en el receptor, el BER se obtiene dividiendo el número de bits errados en la transmisión por el largo total de la secuencia:

(2.12)

$$BER = \frac{\text{Número de bits erróneos}}{n}$$

Con los parámetros  $E_b/N_0$  y BER es posible comparar esquemas de modulación digital o codificación. A modo de ejemplo, una secuencia de tramas de bits moduladas en BPSK requiere un nivel de potencia  $E_b/N_0 = 4.30$  [dB] para obtener un BER promedio de  $10^{-2}$  (1 bit errado por cada 100 enviados); para lograr dicha tasa de errores con tales secuencias moduladas en BFSK, la potencia necesaria es de  $E_b/N_0 = 8.91$  [dB]. En conclusión, para

$<sup>^5{\</sup>rm En}$ adelante se denomina BPSK al esquema PSK binario con modulación no diferencial y demodulación coherente.

obtener en promedio la misma cantidad de errores, modular la secuencia en BFSK redunda en un mayor consumo de potencia comparado a BPSK.

Es importante señalar que, bajo un sistema digital de comunicaciones sin codificación, el BER converge a la probabilidad de error  $P_b$  dada por el esquema de modulación empleado, a medida que aumenta la cantidad de transmisiones de secuencias binarias. Esto pues ambos indicadores son relativos al demodulador. En un esquema de comunicaciones con codificación esto no es así, puesto que el BER se mide entre la secuencia binaria inicial y la secuencia final decodificada; en tal caso se está midiendo el desempeño del decodificador y del demodulador en su conjunto.

### 2.3.4. Ganancia de código

Este indicador señala el ahorro energético consecuente al uso de un esquema de codificación comparado con otro, o con un esquema de transmisión no codificado, para una tasas de errores determinada. Para este último caso, con BER fijo  $P_e$  se tiene que la ganancia de código es:

(2.13)

$$\Delta G|_{\text{BER}=P_e} = \left[ \left( \frac{E_b}{N_0} \right)_{\text{No codificado}} - \left( \frac{E_b}{N_0} \right)_{\text{Codificado}} \right]_{\text{BER}=P_e}$$

Si se comparan dos esquemas de codificación en la ecuación anterior, la razón  $E_b/N_0$  no codificado será el del esquema codificado con mayor potencia requerida para  $P_e$ .

## 2.4. Comunicaciones satelitales

## 2.4.1. Descripción general

En el campo de las comunicaciones satelitales, se distinguen diversas órbitas con fines y aplicaciones diferentes. Estas órbitas varían principalmente en cuanto a la altitud de ubicación, desde los sistemas geoestacionarios GEO (Geostationary Earth Orbit) con altitud promedio de 36.000 [Km] desde la Tierra, hasta los sistemas de baja órbita LEO (Low Earth Orbit) con altitud variable entre 300 y 800 [Km]. Otras órbitas se diferencian por inclinación respecto del Ecuador, excentricidad y sincronía relativa a alguna referencia como el Sol. La órbita de interés del satélite Cubesat SUCHAI es una órbita LEO polar, es decir que cruza la Tierra con inclinación de alrededor de 90° respecto al Ecuador.

#### Subsistemas de enlaces satelitales

A grandes rasgos, un sistema de comunicaciones satelital consiste de dos segmentos principales:

- Estación terrestre: Se ubica en la superficie terrestre, en zonas fijas o vehículos móviles, y su propósito es comunicarse con el satélite, mediante equipamiento como: antenas, amplificadores, equipos de procesamiento (modulación y demodulación, codificación y decodificación, ecualización), equipos de control, etc.

- Satélite: Dispone de varios subsistemas, con dimensiones limitadas a la del mismo satélite, que responden a las necesidades y requerimientos específicos del mismo. Los principales subsistemas son [41, Cap. 3]:

- 1. Antenas: su función es recibir y transmitir señales en radiofrecuencia hacia o desde las zonas de cobertura deseadas.

- 2. Comunicaciones: amplifican las señales recibidas, cambian su frecuencia y la entregan a la(s) antena(s) para su retransmisión a la Tierra. Puede incluir conmutación y procesamiento de señales (multiplexión/demultiplexión, codificación de fuente y/o canal, encriptación).

- 3. Energía eléctrica: Suministra electricidad a todos los equipos, con los niveles adecuados de voltaje y corriente, bajo condiciones de iluminación solar o eclipse.

- 4. Control térmico: regula la temperatura del conjunto, dada su gran fluctuación entre los periodos de iluminación y eclipse.

- 5. Posición y orientación: determina y mantiene la posición y/u orientación del satélite. Estabiliza y orienta correctamente las antenas y paneles de celdas solares.

- 6. Propulsión: proporciona incrementos de velocidad y torques para corregir las desviaciones en posición y orientación.

- Rastreo, telemetría y comando: intercambia información con la estación terrestre en Tierra para observar el funcionamiento del satélite. Monitoreo del estado del mismo.

- 8. Estructural: aloja todos los equipos y le da rigidez al conjunto, en el lanzamiento y en su órbita de funcionamiento.

En el caso de satélites comerciales, en general se prescinde de procesamiento de señales, actuando sólo como repetidores entre dos o más estaciones terrestres. En satélites con fines de investigación, se incluye instrumentación adicional para experimentos, conocida genéricamente como  $payload^6$ .

<sup>&</sup>lt;sup>6</sup>También denominada carga científica.

#### Subsistemas del satélite SUCHAI

El satélite SUCHAI no requiere mecanismos de propulsión, pues es eyectado en su órbita por un dispositivo conocido como P-POD, diseñado con ese objetivo. El subsistema de posicionamiento es opcional, y se analiza la inclusión de componentes que responden al magnetismo de la Tierra para la orientación, llamados magneto-torquers.

Se emplea una única antena dipolo, la cual se despliega en una de las caras del satélite tras un lapso de tiempo posterior a la eyección del CubeSat. Su fuente energética la constituyen celdas solares, funcionales en los ciclos donde el satélite recibe radiación solar, y baterías que reservan energía para su disponibilidad en los ciclos de oscuridad (ciclos llamados *eclipses*).

Se realiza también procesamiento de señales, centralizados en la unidad OBC (On Board Computer), concebida como un subsistema aislado de Comunicaciones, en contraste a lo señalado en la lista anterior. El subsistema de comunicaciones enlaza el procesamiento de datos con la transmisión y recepción mediante la antena, mediante un protocolo adecuado que incluyen corrección y detección de errores, modulación BFSK, y retransmisión de datos [3]. La telemetría y telecomandos constituyen parte de los subsistemas OBC y comunicaciones.

Se incluyen payloads para realizar diversos estudios. Uno lo constituye el estudio del plasma en la ionosfera, mediante el sensor Langmuir. Otro experimento está orientado al estudio del comportamiento de partículas en ambiente de microgravedad. Otros experimentos están en etapa de estudio para su posible inclusión en esta misión.

Finalmente, el cuerpo del CubeSat está constituido por una estructura cúbica de 10 [cm] de longitud, armado mediante la unión de aristas que dan forma a las caras y vértices del cubo; este armado es suficiente para dar la rigidez necesaria al sistema, además de reducir el peso y dejar huecos en las caras que permiten la colocación de los paneles solares, el subsistema de antena, y los *payloads*.

# 2.4.2. Descripción de enlaces de baja órbita

Un enlace satelital de baja órbita se distingue por las siguientes características:

- 1. El tiempo de enlace entre la estación terrestre y el satélite es bastante reducido, debido a que a menor altura la velocidad tangencial para mantener al satélite en la órbita deseada aumenta. En el caso de la órbita polar, se debe considerar que mientras el satélite se mueve longitudinalmente, la Tierra rota, por lo que la probabilidad de que pase sobre la estación terrestre, disminuye a una o dos veces al día, con tiempos de paso breve (10 minutos o menos) y, en general, con ángulos de elevación bajos, por lo que se empobrece el enlace en cuanto a niveles de potencia y cantidad de información enviada o recibida.

- 2. Debido a la alta velocidad orbital del satélite, se produce efecto Doppler en la señal de enlace. En la banda de frecuencias UHF (entre 300 y 3000 [MHz]), el desplazamiento en

frecuencia puede alcanzar los 10 [kHz] [32]. Este efecto se puede corregir si se conocen la altura y velocidad tangencial del satélite.

- 3. El tamaño del satélite impone restricciones a los subsistemas importantes como Energía y Comunicaciones. En el caso de Energía, la alimentación por energía solar se ve limitada al tamaño reducido de las placas solares; en el caso de las Comunicaciones, la potencia de la señal es limitada, y las antenas aptas para esta aplicación ofrecen baja ganancia, tanto por su tamaño como por su baja direccionalidad. Estas restricciones son propias de satélites pequeños, incluyendo *Cubesats*.

- 4. Dependiendo de la capa atmosférica donde el satélite está en órbita, existen diversos efectos que distorsionan la señal. El principal es el efecto Faraday que se produce en la ionosfera, que consiste en la rotación del plano de polarización. El vector de campo eléctrico puede girar hasta 150° en la banda UHF [41, Cap. 5]. Otro fenómeno presente es el centelleo (scintillation), fluctuaciones rápidas de amplitud, fase y ángulo de recepción de las ondas, producido por los cambios en el índice de refracción en la troposfera [41, Cap. 5]. La absorción atmosférica es de escasa importancia, pues las frecuencias de resonancia de elementos como agua, oxígeno y dióxido de carbono son importantes a partir de los 22 [GHz]. La lluvia, las nubes y la neblina son de importancia en frecuencias sobre 10 [GHz]; la degradación está ligada en tal caso al tamaño relativo de las gotas con respecto a la longitud de onda (en el caso del Cubesat λ ≈ 68 [cm] para 435 [MHz]) [41, Cap. 5]. Por último, si se compara un satélite en baja órbita con un sistema satelital a mayor altitud, el primero pierde menos potencia por dispersión.

Estos factores en conjunto inciden en la calidad de la transmisión, degradando la señal. Esto representa un problema en el caso de SUCHAI, pues puede perturbar tanto la transmisión hacia el satélite de telecomandos que ejecuten las acciones requeridas, como la recepción de señales en la estación terrena, que deben contener información fiable del estado del satélite y de los datos de los *payloads*. Es por ello que el dispositivo de comunicaciones implementa corrección de errores para los telecomandos, y detección de tramas erróneas en telemetría que efectúe la retransmisión de ellas.

El problema expuesto plantea la necesidad de implementar sistemas de control de errores, para enlaces de subida (uplink) o de bajada (downlink). A pesar de que esta misión agrega tal sistema, es deseable estimar su desempeño efectivo, y a la vez estudiar otras alternativas de corrección y/o detección de errores para un futuro dispositivo de comunicaciones.

## 2.5. Codificación para control de errores

## 2.5.1. Esquemas de control de errores

Debido a las características enumeradas en la sección 2.4.2, en un canal de comunicaciones de baja órbita puede ser una ventaja implementar algún sistema de protección

de la información que disminuya la tasa de errores en la transmisión o recepción. Esto es importante para la transmisión de datos experimentales hacia la estación terrestre, así como para evitar errores en los telecomandos.

Existen dos esquemas principales que manejan los errores introducidos por el canal. El primero consiste en un esquema de repetición, denominado ARQ (Automatic Repeat reQuest), y consiste en reenviar una trama de datos o telecomandos, si tras un tiempo de espera llamado timeout, el transmisor no ha recibido una trama específica conocida como acknowledgment, notificando que el receptor ha recibido correctamente el comando enviado. Esta situación se repite hasta que el transmisor reciba el acknowledgment. Otro mecanismo de control de errores es el uso de codificación de canal, denominado FEC (Forward Error Correction). Éste se basa en la extensión del mensaje agregando símbolos de redundancia en función de algún algoritmo implementado en el codificador. Al ser recibido, dicho mensaje extendido pasa por el decodificador, que verifica el mensaje original y corrige los errores introducidos por el canal, en función de su capacidad de corrección intrínseca. La ventaja del esquema FEC sobre el ARQ es que permite realizar corrección sin reenvío de información, y su capacidad de corregir errores puede incrementarse dependiendo del esquema de codificación. Estas razones justifican el amplio uso de este mecanismo de control de errores en enlaces satelitales.

#### 2.5.2. Códigos lineales de bloques

Los códigos lineales de bloques corresponden informalmente a un conjunto de estrategias que forman parte del mecanismo de control de errores FEC. Tales estrategias reciben también la denominación de esquemas de codificación. Cada esquema en particular agrega redundancia al mensaje original mediante algún algoritmo específico, lo cual es aprovechado en el receptor para recuperar el mismo de la forma más fidedigna posible.

Todo esquema de codificación se desarrolla a partir de las propiedades del álgebra lineal y la teoría de campos finitos, por lo que es posible establecer sus cualidades específicas analizando su estructura y propiedades algebraicas, en el contexto dado por algunos conceptos propios del ámbito de Codificación, presentados más adelante. Esto debe incluir la modelación del canal, que permite estimar el comportamiento real de tales códigos. La teoría y propiedades del álgebra lineal, y la teoría de campos finitos con sus consecuencias en la constitución de códigos lineales, pueden ser revisados con detalle en la literatura [9], [11], [13], [40], [57]. La revisión dada en este Capítulo pretende sólo establecer los elementos necesarios para su aplicación posterior.

La siguiente es una definición operacional de los códigos lineales de bloques.

**Definición 2.5.1** Un código lineal de bloques, de tamaño M sobre un alfabeto de q-símbolos es un conjunto de M secuencias q-arias de largo n , llamadas palabras de código, que son transmitidos a través de algún canal determinado.

Usualmente  $M = q^k, k \in \mathbb{Z}$  y q = 2, es decir el alfabeto es binario [9]. El espacio vectorial

algebraico donde residen estos códigos se denomina **campo de Galois**<sup>7</sup>, y denotado por  $GF(q)^n$  bajo la descripción anterior.

Bajo la definición previa, queda explícita la diferencia entre un código lineal, entendido como un conjunto de palabras de código, y un esquema de codificación, que corresponde a la estrategia de asignación de tales palabras de código para cada mensaje, y su posterior recuperación mediante un algoritmo de decodificación. Es posible hallar en la literatura el uso indistinto del término *código* para ambos conceptos, pero debe tenerse en cuenta esta diferencia conceptual expuesta.

Existen varios esquemas de códigos lineales, distinguidos por sus propiedades algebraicas y formas de construcción; esto conlleva diversos desempeños para cada uno de ellos que dependen también del canal donde son aplicados. Del mismo modo, cada uno se caracteriza matemáticamente de forma distinta, pero siempre se podrán representar equivalentemente como operaciones matriciales y vectoriales, como se indica posteriormente.

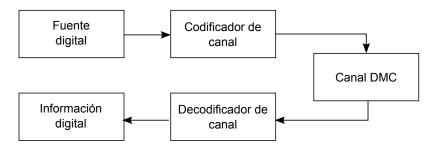

Bajo la definición 2.5.1, para el caso de un alfabeto binario, una palabra de código lineal de largo n representa un bloque de información de largo k codificado. El conjunto de todas las palabras de código conforman un conjunto denotado C(n,k). Es decir, un mensaje de bits de largo k es proyectado en una secuencia de largo n, la cual se transmite por el canal. En el extremo receptor, el decodificador recibe la secuencia alterada por el canal, y es decodificado en un mensaje de largo k que es una estimación del original. Esto se muestra gráficamente en la Figura 2.9. Además, dados los parámetros n y k, se describe un código de bloque por la llamada tasa de codificación R = k/n; con ella se conoce la proporción del mensaje en la secuencia transmitida con respecto al largo total de esta última. Por último, si la transmisión de símbolos es a una tasa de 1/T [símbolos/segundo] (baud rate) en un sistema codificado, la información comunicada tiene una tasa de datos de R/T [símbolos/segundo].

Figura 2.9: Codificación de bloques.

La tabla 2.1 ilustra las operaciones en el alfabeto binario, el cual se denota por  $GF(2)^n$ , siendo n el largo de las palabras de código. Las operaciones se llevan a cabo bit a bit. Una excepción importante la conforman los códigos lineales llamados Reed-Solomon [48], cuyos alfabetos tienen más de dos elementos por definición, y por tanto su operatoria algebraica es diferente.

<sup>&</sup>lt;sup>7</sup>Traducido del inglés Galois field

| + | 0 | 1 | x | 0 | 1 |

|---|---|---|---|---|---|

| 0 | 0 | 1 | 0 | 0 | ( |

| 1 | 1 | 0 | 1 | 0 | 1 |

Tabla 2.1: Operaciones en GF(2).

**Definición 2.5.2** La distancia de Hamming entre dos palabras de código corresponde al número de símbolos en que ambas difieren. La distancia mínima de un código,  $d_{min}$ , es la mínima distancia entre dos palabras del código [9].

Como ejemplo, si se tienen las palabras de código  $c_1 = [0 \ 1 \ 1 \ 1 \ 0] \ y \ c_2 = [0 \ 1 \ 0 \ 0 \ 0]$ , ambas difieren en el tercer y cuarto símbolo; por lo tanto, la distancia Hamming entre ambas palabras es d = 2. Notar que la distancia de Hamming es una métrica y, por consiguiente, cumple las propiedades respectivas (no-negatividad, simetría, desigualdad triangular).

**Definición 2.5.3** El **peso de Hamming** de una palabra de código v es el número de símbolos distintos de '0' en v. El **peso mínimo** corresponde al menor peso de Hamming entre las secuencias pertenecientes a un código lineal, excluyendo aquella que contiene sólo símbolos '0'.

Los conceptos de distancia y peso permiten caracterizar cualquier código de bloques. Más aún, son indistinguibles en el caso de distancia y peso mínimos, como establece el siguiente Teorema.

**Teorema 2.5.1** La mínima distancia de Hamming en un código lineal de bloques es igual al peso mínimo de sus palabras de código [13, Cap. 3].

**Definición 2.5.4** La capacidad de corrección es una medida de cuántos errores es posible corregir en una palabra de código. En general para un código lineal C(n, k), la capacidad t será un entero que satisfaga [11, Cap. 2]:

$$(2.14) 2t + 1 \le d_{min} \le 2t + 2$$

Donde  $d_{min}$  es la distancia mínima de Hamming.

De la ecuación 2.14 se infiere que la capacidad de corrección se incrementa con la distancia mínima. Esto es intuitivo si se observa que cuanto mayor es esta distancia, es más fácil diferenciar entre palabras de código, descontando el efecto alterador del canal.

En algunas aplicaciones puede ser de interés sólo detectar las secuencias erróneas, solicitando al transmisor el reenvío de las mismas. En tal caso, se requiere conocer la sensibilidad del receptor para detectar los errores en los códigos enviados. El concepto definido a continuación permite cuantificar dicha sensibilidad.

**Definición 2.5.5** La capacidad de detección mide cuántos errores es posible detectar en una palabra de código. En un código lineal C(n,k), la capacidad de detección  $d_{det}$  es [13, Cap. 3]:

$$(2.15) d_{det} = d_{min} - 1$$

Donde  $d_{min}$  es la distancia mínima de Hamming.

De las ecuaciones 2.14 y 2.15 se infiere que en los códigos lineales de bloque la capacidad de detección  $d_{\text{det}}$  es al menos dos veces mayor que la capacidad de corrección t. Por consiguiente, si se emplea un esquema con una capacidad de corrección adecuada para un canal determinado, puede ser de utilidad añadir un sistema de retransmisión que aproveche la detección de secuencias erradas, si la situación lo amerita.

#### Descripción matricial de códigos lineales

Los códigos lineales pueden ser representados por operaciones algebraicas con vectores y matrices. De este modo, si en un codificador ingresa una palabra de datos de largo k bits, se representa tal palabra mediante un vector fila a de k-componentes, y se mapea dicho vector a una palabra de código c de n-componentes mediante la denominada **matriz generadora** G, de dimensión  $k \times n$ . Luego la operación ejecutada en el codificador es

$$(2.16) c = a\mathbf{G}$$

Todo código lineal puede ser descrito por la matriz **G**. Esto tiene la ventaja concreta de poder construir codificadores a partir de bloques lógicos digitales.

Análogamente, en el extremo receptor, la llamada matriz de chequeo de paridad  $\mathbf{H}$  es tal que permite comprobar si la palabra de código recibida v corresponde en efecto a la original transmitida, mediante el producto

$$(2.17) v\mathbf{H}^T = z$$

El vector z obtenido de esta operación se denomina **síndrome**, y es el mecanismo más básico para detectar y/o corregir errores en las secuencias recibidas. Tal mecanismo se llama detección de síndrome.

Cuando el síndrome es no nulo se tiene que la palabra de código ha sufrido perturbaciones en el canal. Si el producto es nulo implica que v es una palabra de código que pudo ser generada por la matriz  $\mathbf{G}$ , aunque puede ser una palabra erróneamente producida por el canal mismo, a partir de una palabra original distinta (ver Figura 2.10). Esto implica que toda secuencia errónea que tenga la forma de una palabra de código queda fuera de la detección y por lo tanto no se puede corregir mediante chequeo de síndrome.

Si el síndrome es nulo y corresponde en efecto a una palabra de código, se cumple la siguiente relación:

$$(2.18) z\mathbf{H}^T = c\mathbf{H}^T = 0$$

De la ecuación 2.16 se tiene que

$$(2.19) c\mathbf{H}^T = a\mathbf{G}\mathbf{H}^T = 0$$

Esto implica que (asumiendo  $a \neq 0$ ):

$$\mathbf{G}\mathbf{H}^T = 0$$

Figura 2.10: Detección de síndrome en el decodificador.

Cuando un código lineal es representado por una matriz generadora  $\mathbf{G}$ , existen muchas matrices  $\mathbf{H}$  posibles. Una manera de obtener fácilmente una matriz de chequeo, dada una matriz generadora, es mediante una forma equivalente de representar los códigos lineales; la matriz  $\mathbf{G}$  puede ser re-escrita como

$$\mathbf{G} = [\mathbf{P} \quad \mathbf{I}_k]$$

donde  $\mathbf{I}_k$  es una matriz identidad de  $k \times k$ , y  $\mathbf{P}$  es de  $k \times (n-k)$ . Esta reformulación de  $\mathbf{G}$  es posible mediante operaciones fila elementales o permutación de columnas, y la matriz resultante produce un código equivalente al original [9, Cap. 3]. Esta forma de  $\mathbf{G}$  se denomina forma sistemática de la matriz generadora. Un codificador que genera palabras de código con la matriz  $\mathbf{G}$  en su forma sistemática se denomina codificador sistemático; y en caso contrario será no-sistemático.

Dada la ecuación previa, se deduce fácilmente una expresión para H, pues

(2.22)

$$\mathbf{G}\mathbf{H}^T = [\mathbf{P} \quad \mathbf{I}_k][\mathbf{I}_{n-k} \quad \mathbf{P}^T] = -\mathbf{P} + \mathbf{P} = 0$$

de donde

$$(2.23) \mathbf{H} = [\mathbf{I}_{n-k} \quad \mathbf{P}^T]^T$$

Como consecuencia inmediata de la codificación sistemática, cuando una palabra de datos es codificada mediante dicha forma matricial, la palabra de código resultante contendrá los bits de redundancia en los primeros n-k bits, seguida de la misma palabra de datos en los k bits posteriores  $^8$ . Por otra parte, es conocido que todo código lineal es equivalente a otro cuyo codificador es sistemático [9]; por lo tanto, si dicho equivalente es conocido, se reduce la complejidad del codificador al asignar palabras de código mediante la sola concatenación de símbolos redundantes, además de simplificar el hallazgo de la matriz de chequeo  $\mathbf{H}$ .

#### 2.5.3. Esquemas de codificación más conocidos

#### Códigos Hamming

Este esquema constituye uno de los primeros códigos lineales estudiados. Fueron descubiertos por R. Hamming en 1950, quien junto a C. Shannon estableció las bases de la teoría del control de errores [27]. Un código Hamming, cuyos mensajes son de largo k y las palabras de código son de largo n, debe satisfacer que  $n=2^m-1$  y  $k=2^m-m-1$ , con  $m\geq 3$ . La decodificación se realiza mediante detección de síndrome. La capacidad mínima de corrección de los códigos Hamming es t=1, para m=3. Una aplicación usual de estos códigos es el Hamming extendido, que añade un bit de redundancia al código Hamming(7,4), convirtiéndolo en Hamming(8,4) capaz de corregir un error y detectar dos, método denominado SECDED (Single error correction, double error detection) y utilizado en memorias D-RAM [42].

#### Códigos cíclicos

Descubiertos por Prange en 1957 [43], un código cíclico es generado al rotar las posiciones de una palabra de código dada, es decir, si se tiene una palabra de código  $c = (c_0, c_1, ..., c_{n-1})$ , la rotación *i*-ésima del mismo dada por  $c^{(i)} = (c_{n-i}, c_{n-i+1}, ..., c_{n-1}, c_0, c_1, ..., c_{n-i-1})$  es también una palabra de código. Es usual describir estos códigos como polinomios en una variable implícita X, donde el coeficiente *i*-ésimo corresponde al bit *i*-ésimo de la palabra de código, y el exponente de la variable es la posición de tal bit.

Como ejemplo, si se tiene la palabra de código c=(1,1,0,1), ésta se representará polinomialmente como  $p(X)=1+X+X^3$ . El grado máximo del polinomio representante de una secuencia es n-1, donde n es el largo de dicha secuencia [11].

Al rotar las posiciones de una misma palabra de código, en algún momento se genera un polinomio equivalente que tiene el mínimo grado entre todas las rotaciones. Dicha secuencia es el **generador polinomial** del código, y basta multiplicarlo por  $X^i$  para obtener la rotación i-ésima del mismo. Siendo códigos de bloque, los cíclicos se pueden describir con una matriz generadora G y una de chequeo de paridad H, donde la matriz G estará formada por los generadores polinomiales rotados de posición. Estas matrices también pueden escribirse de

<sup>&</sup>lt;sup>8</sup>En un canal con errores de ráfaga, la transmisión de una trama codificada en forma sistemática podría dañar sucesivamente varios bits de redundancia o de información, produciendo una tasa mayor de errores. Esto puede evitarse añadiendo un *entrelazador* que distribuya uniformemente los bits en la secuencia antes de ser transmitidos.

forma sistemática. En cuanto a la decodificación puede utilizarse la detección de síndrome, pero existen mejores algoritmos que aprovechan la estructura cíclica del código como el algoritmo de Meggit [37] o el de captura de error [13].

Este esquema es utilizado en el estándar Ethernet, en el llamado código de redundancia cíclica (CRC), que forma parte del *data frame* del protocolo; tal mecanismo consiste en añadir al bloque de datos una redundancia de 32 bits mediante un polinomio generador conocido [11, Cap. 3].

#### Códigos BCH

El esquema BCH (Bose, Chaudhuri [10], Hocquenghem [28]) lo constituyen códigos cíclicos cuya característica distintiva es la mejora en la capacidad de corrección de errores, tanto con alfabetos binarios o no-binarios, es decir con dos o más símbolos. En este sentido, son una generalización de los códigos Hamming, pues es posible seleccionar la capacidad de corrección mediante la variación de la tasa de código. Los esquemas BCH deben satisfacer que para todo  $m \geq 3$ ,  $n = 2^m - 1$ . En la Tabla 2.2 se muestra la capacidad de corrección de un código BCH con m = 6:

| k  | t  | R    |

|----|----|------|

| 57 | 1  | 0.90 |

| 51 | 2  | 0.81 |

| 45 | 3  | 0.71 |

| 39 | 4  | 0.62 |

| 36 | 5  | 0.57 |

| 30 | 6  | 0.48 |

| 24 | 7  | 0.38 |

| 18 | 10 | 0.29 |

| 16 | 11 | 0.25 |

| 10 | 13 | 0.16 |

|    |    |      |

Tabla 2.2: Capacidad de corrección t de códigos BCH(n,k) en función de R=k/n con n=63. Tabla extraída de [42]

Estos códigos se extienden a diversas aplicaciones tales como televisión satelital y protección de datos en medios de almacenamiento de estado sólido (discos duros, DVDs, códigos de barra). En particular, en aplicaciones satelitales ha formado parte de estándares de comunicaciones de organizaciones como el CCSDS<sup>9</sup> [18]. El dispositivo de comunicaciones del proyecto SUCHAI emplea un código BCH (63,56) [3], es decir, un BCH (63,57) al cual se le ha eliminado un bit de información, técnica conocida como acortamiento<sup>10</sup>. A la trama resultante de 63 bits se añade un bit '0' que completa una secuencia de 64 bits (8 bytes) [2]. La

<sup>&</sup>lt;sup>9</sup>La revisión del estándar de 2010 ha sido la última donde se incluye este esquema. En revisiones posteriores se ha optado por técnicas más recientes para control de errores.

<sup>&</sup>lt;sup>10</sup>Del inglés shortening.

mejora que introduce esta modificación es la reducción a la mitad de los mensajes posibles en el código original, disminuyendo la cantidad de unidades digitales requeridos en el codificador, tales como flip-flops y sumadores, y requiriendo menor tamaño de buffer para decodificación. Sin embargo, la tasa de código cae de R=0.9 a R=0.88, disminuyendo la cantidad efectiva de datos por trama en la transmisión. De la Tabla 2.2 se aprecia que la capacidad de corrección no aumenta, pues habría que reducir el largo del mensaje a k=51 bits para que t=2. De las Ecuaciones 2.14 y 2.15, no es posible concluir directamente si la capacidad de detección  $d_{\rm det}$  se incrementa, dado que t sólo la acota inferiormente<sup>11</sup>.

#### Códigos Reed-Solomon