Received December 21, 2020, accepted January 14, 2021, date of publication January 25, 2021, date of current version February 8, 2021.

Digital Object Identifier 10.1109/ACCESS.2021.3054340

# **Experimental Validation of a Nested Control System to Balance the Cell Capacitor Voltages** in Hybrid MMCs

FELIPE DONOSO<sup>®1,2</sup>, (Student Member, IEEE), ROBERTO CARDENAS<sup>10</sup>, (Senior Member, IEEE), MAURICIO ESPINOZA<sup>10</sup>, (Member, IEEE), JON CLARE<sup>©</sup>2, (Senior Member, IEEE), ANDRÉS MORA<sup>©</sup>4, (Member, IEEE), AND ALAN WATSON (Member, IEEE)

Department of Electrical Engineering, Faculty of Mathematical and Physical Sciences, University of Chile, Santiago 8370451, Chile

PEMC Research Group, Faculty of Engineering, University of Nottingham, Nottingham NG7 2RD, U.K.

Corresponding author: Roberto Cardenas (rcd@ieee.org)

The work of Felipe Donoso was supported by CONICYT- PCHA/Doctorado Nacional/2016-21160931. The work of Roberto Cardenas was supported by Fondect Nr. 1180879 and Basal Project FB0008. The work of Andrés Mora was supported by Fondecyt Project Nr. 11190852.

**ABSTRACT** In a hybrid modular multilevel converter (MMC), capacitor voltage balance between the Full-Bridge Sub-Modules (FBSMs) and Half-Bridge Sub-Modules (HBSMs) is only possible when the arm currents are bipolar. For a grid-connected MMC, operating at unity power factor, this is typically only achievable when the modulation index is less than 2. Previous control methodologies, based on open-loop feed-forward compensating currents, have been proposed to operate an MMC with a higher modulation index. However, these solutions do not minimize the compensating currents; they cannot compensate entirely for both the variations in the operating conditions and the parameters typically encountered in a real implementation; and they do not consider the actual capacitor voltage imbalance between the FBSM and HBSMs. In this paper, a new nested closed-loop control algorithm based on an outer voltage control loop with an inner current loop is proposed and experimentally validated. Feed-forward currents are still utilised in the inner loop, but they are calculated using a new optimising algorithm which minimises the required compensating currents. Moreover, to the best of our knowledge, this is the first work where explicit algebraic equations to calculate these compensating currents are provided. Experimental results to validate the approach, obtained with an 18-cell hybrid MMC, are presented and discussed in the paper.

**INDEX TERMS** Modular multilevel converters, hybrid MMC, sub-module capacitor balance.

### I. INTRODUCTION

Nowadays, the modular multilevel converter (MMC) is a prominent solution for high voltage direct current (HVDC) transmission systems [1], [2] and for medium voltage drive applications [3], [4]. The main benefits of the MMC are its modularity and scalability to reach high voltage requirements, high efficiency, low harmonic distortion, transformerless operation, and reduced dv/dt in each switch [5], [6].

MMCs are composed of several building blocks termed sub-modules (SM). Various SMs have been proposed to populate MMCs, such as the half-bridge sub-module (HBSM),

The associate editor coordinating the review of this manuscript and approving it for publication was Zhouyang Ren .

the full-bridge sub-module (FBSM) and the neutral-point clamped (NPC) sub-module [7]. However, most MMC applications use the HBSM to reduce semiconductor power losses. In HVDC applications, the main drawback of the HBSM-based MMC is that it cannot control fault currents due to DC short circuits [8]. Consequently, for a pole to pole fault, the freewheel diodes of each HBSM could be damaged [9], [10]. A possible solution, to block the DC short circuits, is to add DC breakers [11] or to change the cell type, for instance, to FBSMs [12]. Another disadvantage of the HBSM-based MMC solution is that it cannot operate with a reduced DC port voltage. During bad weather conditions, it is common practice to reduce the DC-port voltage to reduce the risk of pole-to-pole short circuits [13], [14].

<sup>&</sup>lt;sup>3</sup>Faculty of Engineering, University of Costa Rica, San Pedro 11501-2060, Costa Rica

<sup>&</sup>lt;sup>4</sup>Department of Electrical Engineering, Universidad Técnica Federico Santa Maria, Valparaiso 8370071, Chile

For drive applications based on the MMC, large low-frequency voltage oscillations can occur in the sub-modules at low mechanical speed. Most of the proposed solutions involve the injection of high frequency circulating currents and common-mode voltage [15]. However, the circulating currents can lead to over-sizing the components and the high frequency common-mode voltage can reduce the lifespan of the machine bearings [16]. To decrease the large voltage oscillations a different approach, discussed in some recent publications, is to reduce the dc-port voltage at low mechanical speed [17]-[20]. In [17], a back-to-back MMC composed entirely of FBSMs is proposed to regulate the dc-port voltage. Although this solution reduces the capacitor voltage oscillation at low speed, it doubles the number of switches and consequently the losses are significantly increased. In [18], [19], the dc-port voltage is modulated using series switches. In this case, the mean value of the dc-link is regulated. However, the additional switches have to withstand the rated dc-port voltage. In addition, snubber filters have to be included to reduce the dv/dt introduced by the series switches.

The hybrid MMC, composed of both HBSMs and FBSMs, was proposed in [21]. The hybrid MMC is able to operate with a dc-port voltage lower than that achievable with a HBSM-based MMC and it has fewer components than the FBSM-based MMC. However, as demonstrated in [22], when the modulation index is large ( $m \ge 2$ ) corresponding to a low dc-port voltage, the arm currents are unipolar (e.g. are always positive) and in this condition the capacitor voltages of the HBSMs cannot be balanced (see [21]).

Some control strategies have been proposed to compensate the capacitor voltage imbalance between the HBSMs and FBSMs in a hybrid MMC. In [21], balancing is accomplished through forcing a polarity change in the arm current by reducing the power factor at the grid-side and increasing the magnitude of the ac component. In [23], the capacitor voltage balancing is realized by injecting a circulating current; however, [23] does not present explicit expressions to calculate the magnitude of the required current. Moreover, the magnitudes of the required circulating currents are calculated offline assuming that the parameters of the MMC and grid are constant.

To operate with a higher modulation index, a modified sorting modulation scheme was introduced in [13]. In this case a PI controller regulates the energy exchange between the HBSMs and FBSMs by changing the order in which the FBSMs are inserted by the modulation scheme, however, this method, even though it is more efficient than others proposed in the literature, does not guarantee the change of polarity in the arm current required to balance the HBSMs at every possible operating point.

The main drawback of the methods discussed in [13], [21], [23], [24] is that the feed-forward circulating currents are calculated off-line and are imposed without considering the degree of imbalance between the capacitor voltages of the FBSMs and HBSMs, i.e., there is no closed-loop

control of the FBSM-HBSM capacitor voltage imbalance, and the system lacks the capability to compensate for changes in the operating point and/or variations in the parameters of the hybrid MMC. Consequently, the off-line calculated feed-forward currents may not be totally effective in dealing with the imbalance.

Considering the problems mentioned above, this paper proposes the use of a nested closed-loop control system to regulate the capacitor voltage imbalances between the HBSMs and FBSMs. To augment the dynamic performance of the proposed control system, off-line calculated compensating currents are also fed-forward to the current control system. The feed-forward currents are based on either reactive grid-current components or internal circulating current components (which do not appear at the grid). The two strategies are denoted as CLC-I and CLC-II (Closed-Loop Control) respectively. The compensating currents are calculated off-line using a methodology based on an optimising algorithm and, therefore, the injected current is the minimum that ensures voltage balance between the FBSMs and HBSMs. The main contributions of this work are:

- 1) Unlike previous works [9], [23], [24] the proposed strategy implements a nested closed loop control system to regulate the FBSM-HBSM capacitor voltage imbalance. An outer control loop acts on the voltage imbalance FBSM-HBSM and an inner control loop regulates the compensating current in the MMC (based on either the CLC-I or CLC-II strategy). Imprecision in the feed-forward terms, due for example to parameter variations are dealt with by the outer closed loop. In this way balance is guaranteed for all operating conditions, with minimum additional current and consequently with minimum additional power loss. The advantage gained by adopting an outer closed loop is significant. Without it, the feed-forward compensating currents would always have to be over specified to guarantee balance in a practical system. To the best of our knowledge this approach has never been presented in the literature.

- The design of this outer control loop is discussed in Section V and its performance is experimentally validated in Section VII-F.

- 2) A new methodology to obtain the feed-forward compensating currents is proposed in this work. It is based on an optimisation problem which is solved numerically (off-line) to reduce the magnitudes of these compensating currents, for either the CLC-I or CLC-II strategy, reducing the losses and thermal stress in the switches. This is discussed in Section IV.

- 3) Unlike previous works [21]–[23], in this paper mathematical expressions for the magnitude of the reactive or circulating current required to guarantee the balance between HBSMs and FBSMs are derived (see the Appendix). To the best of our knowledge, explicit equations to calculate the feed-forward compensating currents have never been presented in the literature

before. Therefore, the methodology presented in this work is straightforward for others to replicate.

4) The advantages and disadvantages of the strategies CLC-I or CLC-II are discussed and compared in Section IV-C and the analysis is experimentally validated. The main conclusions drawn from this comparison can be generalised to most of the strategies based on circulating currents and/or reactive current compensation, reported in the literature [21]–[23].

The rest of this paper is organised as follows: the analytical model of the hybrid MMC is presented in Section II. Section III introduces the capacitor voltage imbalance problem in a hybrid MMC. The proposed strategies are explained in Section IV. The outer and inner control loops proposed in this paper are presented in Section V. Section VI briefly discusses the global balancing control. Experimental results are analysed and discussed in Section VII. The conclusions are presented in Section VIII. Finally, there is an Appendix where the algebraic equations for the CLC-I and CLC-II methods are given.

#### II. MODELLING OF THE HYBRID MMC

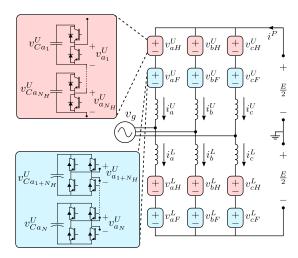

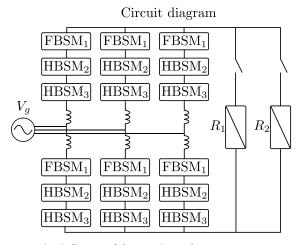

The hybrid MMC consists of six arms as depicted in Fig. 1. Each arm is composed of the cascaded connection of N sub-modules and an inductor L. In each arm there are  $N_H$  HBSMs and  $N_F$  FBSMs, with  $N = N_H + N_F$ .

FIGURE 1. Circuit diagram of the hybrid MMC.

For the hybrid MMC shown in Fig. 1, each output phase  $x \in \{a, b, c\}$  is connected to an upper (U) and lower (L) arm designated as  $y \in \{U, L\}$  respectively. The voltage modulated by each arm  $v_x^y$  is depicted in (1), where  $S_{xHi}^y \in \{0, 1\}$  and  $S_{xFi}^y \in \{-1, 0, 1\}$  are the switching states for the HBSMs and FBSMs respectively, and  $v_{Cx_i}^y$  is the capacitor voltage of the  $i_{th}$  cell of phase x and arm y.

$$v_x^y = v_{xH}^y + v_{xF}^y = \sum_{i=1}^{N_H} v_{Cx_i}^y S_{xHi}^y + \sum_{i=N_H+1}^N v_{Cx_i}^y S_{xFi}^y$$

(1)

The voltage-current relationships of the hybrid MMC are shown in (2) using natural coordinates, where E is the dc-port voltage,  $v_x^y$  and  $i_x^y$  are the arm voltages and currents respectively, and  $v_x$  is the grid voltage.

$$\frac{E}{2} \begin{pmatrix} 1 & 1 & 1 \\ 1 & 1 & 1 \end{pmatrix} = \begin{pmatrix} v_a^U & v_b^U & v_c^U \\ v_a^L & v_b^L & v_c^L \end{pmatrix} + \begin{pmatrix} v_a & v_b & v_c \\ -v_a & -v_b & -v_c \end{pmatrix} + L \frac{d}{dt} \begin{pmatrix} i_a^U & i_b^U & i_c^U \\ i_a^L & i_b^L & i_c^L \end{pmatrix} \tag{2}$$

Notice that in (2) the Thevenin inductance of the grid is considered negligible. The variables in (2) are coupled and, consequently, it is not straightforward to independently control the outer and inner converter variables in this reference frame. To overcome this problem, some authors have proposed the use of the  $\Sigma\Delta\alpha\beta0$  linear transformation [25], [26]. Given a matrix in the natural coordinates  $X_{abc}^{UL}$ , its  $\Sigma\Delta\alpha\beta0$  transformation is obtained by pre-multiplying it by  $T_{\Sigma\Delta}$  and post-multiplying it by  $T_{\alpha\beta0}$ . For instance, the arm voltage  $V_{\alpha\beta0}^{\Sigma\Delta}$  is calculated as:

$$\underbrace{\begin{pmatrix} v_{\alpha}^{\Sigma} & v_{\beta}^{\Sigma} & v_{0}^{\Sigma} \\ v_{\alpha}^{\Delta} & v_{\beta}^{\Delta} & v_{0}^{\Delta} \end{pmatrix}}_{V_{\alpha}^{\Sigma\Delta}} = T_{\Sigma\Delta} \underbrace{\begin{pmatrix} v_{a}^{U} & v_{b}^{U} & v_{c}^{U} \\ v_{a}^{L} & v_{b}^{L} & v_{c}^{L} \end{pmatrix}}_{V_{\alpha}^{UL}} T_{\alpha\beta0} \quad (3)$$

where the matrices  $T_{\Sigma\Delta}$  and  $T_{\alpha\beta0}$  are defined by:

$$T_{\Sigma\Delta} = \frac{1}{2} \begin{pmatrix} 1 & 1 \\ 2 & -2 \end{pmatrix} \quad T_{\alpha\beta0} = \frac{1}{3} \begin{pmatrix} 2 & 0 & 1 \\ -1 & \sqrt{3} & 1 \\ -1 & -\sqrt{3} & 1 \end{pmatrix}$$

(4)

Applying the  $\Sigma \Delta \alpha \beta 0$  transformation to (2), the following decoupled model is obtained:

$$\frac{E}{2} \begin{pmatrix} 0 & 0 & 1 \\ 0 & 0 & 0 \end{pmatrix} = \begin{pmatrix} v_{\alpha}^{\Sigma} & v_{\beta}^{\Sigma} & v_{0}^{\Sigma} \\ v_{\alpha}^{\Delta} & v_{\beta}^{\Delta} & v_{0}^{\Delta} \end{pmatrix} + 2 \begin{pmatrix} 0 & 0 & 0 \\ v_{\alpha} & v_{\beta} & v_{0} \end{pmatrix} + L \frac{d}{dt} \begin{pmatrix} i_{\alpha}^{\Sigma} & i_{\beta}^{\Sigma} & \frac{1}{3}i^{P} \\ i_{\alpha} & i_{\beta} & 0 \end{pmatrix} \quad (5)$$

where instead of using the 6 arm currents  $i_x^y$  in natural coordinates, they are expressed in the  $\Sigma\Delta\alpha\beta0$  reference frame as the dc-port current  $i^P$ , the ac-port currents  $i_{\alpha\beta}$ , which are the  $\alpha-\beta$  components of the grid-current for the circuit depicted in Fig. 1, and the circulating currents  $i_{\alpha\beta}^\Sigma$  (internal to the converter). According to (5),  $i^P$ ,  $i_{\alpha\beta}$ , and  $i_{\alpha\beta}^\Sigma$  can be controlled independently by the arm voltage terms  $v_0^\Sigma$ ,  $v_{\alpha\beta}^\Delta$ , and  $v_{\alpha\beta}^\Sigma$  respectively. Throughout the paper, bold fonts are used to denote vectors.

### A. ENERGY CONTROL OF THE HYBRID MMC

Energy control of the MMC has been addressed in several publications [26], [27], for completeness it is briefly discussed below.

Energy storage of the six arms is indirectly regulated by controlling the total capacitor voltage of each arm:

$$v_{Cx}^{y} = \sum_{i=1}^{N} v_{Cxi}^{y} \quad x \in \{a, b, c\}, \ y \in \{U, L\}$$

(6)

To regulate the total capacitor voltage  $v_{Cx}^y$  with  $x \in \{a, b, c\}$  and  $y \in \{U, L\}$ , the instantaneous power of each arm  $P_{abc}^{UP}$  is controlled:

$$\frac{d}{dt} \underbrace{\begin{pmatrix} v_{Ca}^{U} & v_{Cb}^{U} & v_{Cc}^{U} \\ v_{Ca}^{L} & v_{Cb}^{L} & v_{Cc}^{L} \end{pmatrix}}_{V_{Cabc}^{UL}} \approx \frac{1}{Cv_{C}^{*}} \underbrace{\begin{pmatrix} p_{a}^{U} & p_{b}^{U} & p_{c}^{U} \\ p_{a}^{L} & p_{b}^{L} & p_{c}^{L} \end{pmatrix}}_{P_{abc}^{UL}} \tag{7}$$

where the instantaneous power of each arm is  $p_x^y = i_x^y v_x^y x \in \{a, b, c\}$  and  $y \in \{U, L\}$ , C is the cell capacitance, and  $v_C^*$  is the capacitor voltage reference of each submodule. By expressing the converter power in the  $\Sigma \Delta \alpha \beta 0$  reference frame, i.e. by pre-multiplying (7) by  $T_{\Sigma \Delta}$  and post-multiplying it by  $T_{\alpha \beta 0}$  [see (3)-(4)], it is relatively simple to identify which current components can be used to balance the energy among the six arms:

$$\frac{d}{dt} \underbrace{\begin{pmatrix} v_{C\alpha}^{\Sigma} & v_{C\beta}^{\Sigma} & v_{C0}^{\Sigma} \\ v_{C\alpha}^{\Delta} & v_{C\beta}^{\Delta} & v_{C0}^{\Delta} \end{pmatrix}}_{V_{C\alpha\beta0}^{\Sigma\Delta}} \approx \frac{1}{Cv_{C}^{*}} \underbrace{\begin{pmatrix} p_{\alpha}^{\Sigma} & p_{\beta}^{\Sigma} & p_{0}^{\Sigma} \\ p_{\alpha}^{\Delta} & p_{\beta}^{\Delta} & p_{0}^{\Delta} \end{pmatrix}}_{P_{\alpha\beta0}^{\Sigma\Delta}} \tag{8}$$

If the energy is completely balanced in the hybrid MMC, then the six capacitor voltages in the matrix located at the left-hand side of (7) are identical (i.e.  $v_{Ca}^U = v_{Ca}^L = v_{Cb}^U = \cdots = v_{Cc}^L = Nv_C^*$ ). Considering this and applying  $T_{\Sigma\Delta}$  and  $T_{\alpha\beta0}$ , it is straightforward to conclude that in a balanced converter the total capacitor voltages in the  $\Sigma\Delta\alpha\beta0$  reference frame are  $v_{C\alpha}^\Sigma = v_{C\beta}^\Sigma = v_{C\alpha}^\Delta = v_{C\beta}^\Delta = v_{C0}^\Delta = 0$  and  $v_{C0}^\Sigma = Nv_C^*$ . The capacitor voltage  $v_{C0}^\Sigma$  is related to the total energy stored in the converter and has to be regulated to a nonzero value, while the remaining 5 voltages term regulate the balance among the converter arms. It can be shown that the power terms  $P_{\alpha\beta0}^{\Sigma\Delta}$  can be obtained as (see [25], [26]):

$$p_0^{\Sigma} = \frac{Ei^P}{6} - \frac{1}{4} \Re\{ \mathbf{v}_{\alpha\beta} \mathbf{i}_{\alpha\beta}^c \} \tag{9}$$

$$\boldsymbol{p}_{\alpha\beta}^{\Sigma} = -\frac{1}{4} (\boldsymbol{v}_{\alpha\beta} \boldsymbol{i}_{\alpha\beta})^{c} + \frac{E}{2} \boldsymbol{i}_{\alpha\beta}^{\Sigma} - \frac{1}{2} v_{0} \boldsymbol{i}_{\alpha\beta}$$

(10)

$$\boldsymbol{p}_{\alpha\beta}^{\Delta} = -(v_{\alpha\beta}\boldsymbol{i}_{\alpha\beta}^{\Sigma})^{c} + \frac{E\boldsymbol{i}_{\alpha\beta}}{2} - \frac{2}{3}\boldsymbol{i}^{P}v_{\alpha\beta} - 2v_{0}\boldsymbol{i}_{\alpha\beta}^{\Sigma} \quad (11)$$

$$p_0^{\Delta} = -\Re\{v_{\alpha\beta}(\mathbf{i}_{\alpha\beta}^{\Sigma})^c\} - \frac{2}{3}\mathbf{i}^P v_0 \tag{12}$$

where  $\Re$  and  $(\cdot)^c$  are the real part and complex conjugate operators respectively. The power term  $p_0^\Sigma$  is proportional to the difference between the ac power and the dc power of the hybrid MMC. The power terms  $p_{\alpha\beta}^\Delta$  and  $p_0^\Delta$  represent the power difference between the upper and lower arms while the power terms  $p_{\alpha\beta}^\Sigma$  represent the power flow between the converter phases [25], [26]. Therefore, to regulate the total capacitor voltages  $V_{C\alpha\beta0}^{\Sigma\Delta}$ , different components of the

circulating current  $i_{\alpha\beta}^{\Sigma}$  along with the dc port current are used. By inspecting the power terms  $P_{\alpha\beta0}^{\Sigma\Delta}$  it is straightforward to choose orthogonal current components to produce controllable dc-power terms, to regulate  $V_{C\alpha\beta0}^{\Sigma\Delta}$  of (8). In the following analyses, the circulating current utilised in this work is shown in (13) where  $\theta = \int \omega_g dt$  is the grid voltage angle and the grid voltage is  $\mathbf{v}_{\alpha\beta} = V_g e^{j\theta}$ .

$$\mathbf{i}_{\alpha\beta}^{\Sigma} = \overline{\mathbf{i}_{\alpha\beta}^{\Sigma}} + \mathbf{i}_{dq}^{\Sigma+} e^{j\theta} + \mathbf{i}_{dq}^{\Sigma-} e^{-j\theta}$$

(13)

To regulate the energy balance among the 6 arms, three balancing actions are considered [25]:

- 1) Total energy control: The power term  $p_0^{\Sigma}$  regulates the total energy stored in the converter. The current  $i^P$  or  $i_d$  can be used to regulate  $p_0^{\Sigma}$  (9).

- 2) Vertical balance: To balance the energy between the upper and lower arms, the power terms  $\boldsymbol{p}_{\alpha\beta}^{\Delta}$  and  $p_0^{\Delta}$  are controlled. By replacing the circulating current  $\boldsymbol{i}_{\alpha\beta}^{\Sigma}$  (13) in the power term  $\boldsymbol{p}_{\alpha\beta}^{\Delta}$  (11) it can be noticed that only the negative sequence component  $\boldsymbol{i}_{dq}^{\Sigma} = e^{-j\theta}$  produces a manipulable dc power term with the grid voltage  $\boldsymbol{v}_{\alpha\beta} = V_g e^{j\theta}$ , in this case, the controllable power term is  $V_g \boldsymbol{i}_{dq}^{\Sigma}$ . Analogously, the positive sequence current component  $\boldsymbol{i}_d^{\Sigma}$  produces a manipulable power term in  $\boldsymbol{p}_0^{\Delta}$  (12).

- 3) Horizontal balance: To balance the arm energy between all phases, the power term  $p_{\alpha\beta}^{\Sigma}$  is used. In this case, the second term of (10) is controlled using the component  $i_{\alpha\beta}^{\Sigma}$  of the circulating current (see (13)).

# III. BALANCE BETWEEN THE HBSMs AND FBSMS DURING LOW DC-PORT VOLTAGE

The capacitor voltage imbalance problems produced in a hybrid MMC operating with a high modulation index m have already been reported in [9], [22]–[24]. For completeness they are briefly discussed here.

When a hybrid MMC operates with a reduced dc-port voltage E, the arm currents can become unipolar, i.e. the arm currents will not have zero crossing points. If this condition is not corrected, the capacitor voltages of the HBSMs and FBSMs will diverge continuously. Without loss of generality, the arm currents of phase a can be considered as:

$$i_a^U = \frac{1}{2}i_a + \frac{i^P}{3} \quad i_a^L = -\frac{1}{2}i_a + \frac{i^P}{3}$$

(14)

which, if the losses are neglected yields:

$$Ei^{P} = \frac{3}{2} V_g I_g \cos(\varphi) \tag{15}$$

where  $V_g$  and  $I_g$  stand for the moduli of the grid voltage and current respectively, and  $\varphi$  is the grid power factor angle. By defining the modulation index as  $m=2V_g/E$  and by replacing (15) into (14), the arm currents  $i_a^U$  and  $i_a^L$  are calculated as:

$$i_a^U = \frac{1}{2} I_g \left( \cos(\omega_g t + \varphi) + \frac{m}{2} \cos(\varphi) \right) \tag{16}$$

$$i_a^L = -\frac{1}{2}I_g\left(\cos\left(\omega_g t + \varphi\right) - \frac{m}{2}\cos\left(\varphi\right)\right) \tag{17}$$

From (16)-(17), if the reactive current is zero (i.e.  $\varphi = 0$ ), the arm currents become unipolar for m > 2. Considering that the voltage synthesised by the half-bridge power cells is also unipolar, it is simple to conclude that, when the arm current is also unipolar, the HBSM power flow is unidirectional and their capacitors charge (or discharge) continuously each time the half-bridges synthesise a non-zero voltage.

# IV. OPTIMAL METHODOLOGY TO ENSURE THE LOCAL **BALANCE OF THE HYBRID MMC**

This paper proposes two control strategies to operate the hybrid MMC with high modulation indices (m>2), by forcing polarity changes in the arm currents. As mentioned previously, the arm current can be made bipolar by injecting reactive current or circulating current. Both strategies aim to move energy from the FBSMs to the HBSM and vice versa. To the best of the authors' knowledge, optimal methodologies to minimise the required circulating or reactive currents have not been proposed before. Moreover, this is the first work where explicit algebraic equations to calculate the compensating current are presented.

For the analysis presented below, it is considered that the cascade connections of FBSMs and HBSMs of phase  $x \in$  $\{a, b, c\}$  and pole  $y \in \{U, L\}$  are modelled as two equivalent sub-modules with a capacitor voltage equal to  $v_{Fx}^y$  and  $v_{Hx}^y$ [see (18)-(20)].

$$v_{Hx}^{y} = \frac{1}{N_H} \sum_{i=1}^{N_H} v_{Cx_i}^{y} \quad v_{Fx}^{y} = \frac{1}{N_F} \sum_{i=1+N_H}^{N} v_{Cx_i}^{y} \quad (18)$$

$$v_H^{\Sigma} = \sum_{x,y} \frac{v_{Hx}^y}{6} \quad v_F^{\Sigma} = \sum_{x,y} \frac{v_{Fx}^y}{6}$$

(19)

$$e_{FH} = \overline{v}_F^{\Sigma} - \overline{v}_H^{\Sigma} \tag{20}$$

### A. REACTIVE CURRENT INJECTION METHOD (CLC-I)

The arm current and voltage  $\boldsymbol{i}_a^U$  and  $\boldsymbol{v}_a^U$  in steady-state operation can be expressed as (21)-(22) where  $i_d$  and  $i_q$  are the active and reactive grid-current, and  $\theta = \omega_g t$  with  $\omega_g$  as the grid frequency. It is assumed that the voltages and currents are referred to a synchronous rotating frame orientated along the grid voltage  $v_{\varrho}$ .

$$i_a^U = \frac{i_d}{2} \left( \cos(\theta) + \frac{m}{2} \right) - \frac{i_q}{2} \sin(\theta) \tag{21}$$

$$v_a^U = \frac{E}{2} \left( 1 - m \cos(\theta) \right) \tag{22}$$

To illustrate the local balancing problem between the HBSMs and FBSMs for  $m \ge 2$ , the instantaneous and average value of the capacitor voltages for the HBSMs  $v_{Ha}^U$  and FBSMs  $v_{Fa}^U$ , along with the arm voltage  $v_a^U$  and arm current  $i_a^U$  are shown in Fig. 2, considering  $i_d < 0$  and  $i_q > 0$ . A similar analysis can be performed for the other operating conditions.

In Fig. 2,  $\theta_{v_1} - \theta_{v_2}$  and  $\theta_{i_1} - \theta_{i_2}$  are the zero-crossing angles of the arm voltage  $v_a^U$  and current  $i_a^U$  respectively.

**FIGURE 2.** Sub-module charging and discharging process for CLC-I. Arm voltage  $v_a^U$  (blue), arm current  $i_a^U$  (yellow), capacitor voltage of the equivalent FBSMs  $v_{Fa}^U$  (green) and HBSMs  $v_{Ha}^U$  (red).

Additionally,  $\theta_{F_1}$  and  $\theta_{F_2}$  are the angles at which the arm voltage  $v_a^U$  is equal to the maximum synthesised voltage of the FBSMs:

$$\theta_{\nu_1} = -\cos^{-1}(m^{-1}) \quad \theta_{\nu_2} = -\theta_{\nu_1}$$

(23)

$$\theta_{i_1} = \cos^{-1}\left(-\frac{mi_d}{2\|i_{dq}\|}\right) - \tan^{-1}(i_q, i_d)$$

(24)

$$\theta_{i_2} = 2\pi - \theta_{i_1} + 2\tan^{-1}(i_q, i_d)$$

(25)

$$\theta_{i_2} = 2\pi - \theta_{i_1} + 2\tan^{-1}(i_q, i_d)$$

$$\theta_{F_1} = \cos^{-1}\left(\frac{1}{m} - \frac{N_F v_C^*}{V_g}\right) \quad \theta_{F_2} = 2\pi - \theta_{F_1}$$

(26)

In this paper, the  $i_q$  required to guarantee balance between the HBSMs and FBSMs is calculated by considering that the  $\Delta E$  energy incremented in the FBSMs (while the HBSMs synthesise 0V) is released during  $\theta \leq \theta_{i_2}$ .

1) Initially, between  $\theta_{v_1}$  and  $\theta_{v_2}$  the arm voltage is negative, and only the FBSMs generate voltage while the HBSMs produce 0V. In this case, the FBSMs increase their total energy  $W_F^+$  (27). Although the HBSMs could be inserted, the FBSMs would then modulate an even lower negative voltage and consequently  $W_F^+$  will be higher than the case when the HBSMs produce 0V.

$$W_F^{(+)} = \int_{\theta_{v_1}}^{\theta_{v_2}} v_a^U i_a^U d\theta = -\frac{i_d E}{4\omega_g} \frac{\left(m^2 - 1\right)^{3/2}}{m}$$

(27)

- 2) Next, in the interval between  $\theta_{\nu_2}$  and  $\theta_{F_1}$  the capacitors of the FBSMs will discharge while the HBSMs synthesise 0V since, in this period, the FBSMs have higher priority to be discharged. The energy exchange is  $W_{F1}^{(-)}$  and it is calculated similarly to the previous case, see (49) in the Appendix.

- 3) Finally, from  $\theta_{F1}$  and  $\theta_D$ , the FBSMs alone are not able to synthesise the required voltage and both the FBSMs

and the HBSMs have to be used. As depicted in Fig. 2,  $\theta_D$  is the angle where the FBSMs have finally released the entire energy,  $W_F^+$ , incremented between  $\theta_{\nu_1}$  and  $\theta_{\nu_2}$ . Notice that  $\theta_D \leq \theta_{i2}$ . The energy released in this period, by the FBSMs, is  $W_{F^2}^{(-)}$  see (50) in the Appendix.

To ensure the balance of the FBSMs, the total energy stored during  $\theta_{i1}$  to  $\theta_{v2}$  has to be released between  $\theta_{v2}$  and  $\theta_D$ , i.e.:

$$W_F^{(+)} + W_{F1}^{(-)} + W_{F2}^{(-)} = 0 (28)$$

Therefore, the required  $i_q$  can be calculated from (28) as a function of  $\theta_D$ . In the appendix, the general expression for calculating  $i_q$  is presented in (51). As an example, a simple case is considered assuming m = 2.6;  $N_F/N_H = 0.5$ ; and  $v_C^* = E/N$ . The required reactive current for this operating condition is shown in (29).

$$i_q(\theta_D) = \frac{i_d(-1.2987\theta_D - \sin(\theta_D) + 5.77691)}{\cos(\theta_D) - 0.0183333}$$

(29)

To inject the minimum reactive current that ensures the local balance (28), the following optimisation problem is proposed:

minimize

$$i_q(\theta_D)$$

subject to  $W_F^{(+)} + W_{F1}^{(-)} + W_{F2}^{(-)} = 0$

$\theta_{F_1} < \theta_D < \theta_{i_2}$  (30)

which is numerically solved off-line (using the Nelder-Mead method). The reactive grid-currents are calculated from the result of (30) using (51) in the appendix and are stored in a look-up table as shown in Fig. 5(b).

## B. CIRCULATING CURRENT INJECTION (CLC-II)

Bipolar arm current can also be forced by injecting a quadrature component in the circulating current. In this case, the extra component only appears in the converter arms and affects neither the ac nor the dc ports of the MMC.

The currents components  $i_d^{\Sigma+}$ ,  $i_{dq}^{\Sigma-}$  and  $i_{\alpha\beta}^{\Sigma}$  are employed to balance energy among the 6 arms of the hybrid MMC as discussed before (global capacitor voltage balance). In this work, a quadrature component of the circulating current ( $i_q^{\Sigma+}$ ) is utilised as a degree of freedom to force a polarity change in the arm currents. The circulating current in natural coordinates  $i_{abc}^{\Sigma}$  can be expressed as:

$$\begin{pmatrix}

i_a^{\Sigma} \\

i_b^{\Sigma} \\

i_c^{\Sigma}

\end{pmatrix} = \begin{pmatrix}

i_{GBa}^{\Sigma} \\

i_{GBb}^{\Sigma} \\

i_{GBc}^{\Sigma}

\end{pmatrix} - i_q^{\Sigma +} \begin{pmatrix}

\sin(\theta) \\

\sin(\theta - \frac{2\pi}{3}) \\

\sin(\theta + \frac{2\pi}{3})

\end{pmatrix} \tag{31}$$

where the terms  $i_{GBx}^{\Sigma}$  are the circulating currents used for the global balance, for instance, for phase a:

$$i_{GBa}^{\Sigma} = \overline{i_{\alpha}^{\Sigma}} + (i_{d}^{\Sigma +} + i_{d}^{\Sigma -})\cos(\theta) + i_{q}^{\Sigma -}\sin(\theta) \qquad (32)$$

During steady-state operation the circulating current required to perform the global balance of the capacitor voltages becomes negligible, therefore  $i_{GBx}^{\Sigma} \approx 0$ . The circulating

current  $i_q^{\Sigma+}$  is added to both the upper and lower arm currents. For instance, if a circulating current component  $i_q^{\Sigma+}$  is injected, the arm currents  $i_q^{\nu}$  with  $\nu \in \{U, L\}$  become:

$$i_a^y = \sqrt{0.25i_d^2 + (\pm 0.5i_q + i_q^{\Sigma +})^2} \cos\left(\omega t + \varphi_a^{U,L}\right) + \frac{i^P}{3}$$

(33)

$$\varphi_a^y = \operatorname{atan2}\left(\pm 0.5i_q + i_q^{\Sigma +}, \pm 0.5i_d\right)$$

(34)

According to (33)-(34), the phase shift and magnitudes of the arm currents  $i_x^U$  and  $i_x^L$  could be different. Therefore, the charging/discharging behaviour of the HBSMs and FBSMs of the upper and lower arms is not the same when compensation utilising circulating current is applied. The minimum required current  $i_q^{\Sigma+}$  to guarantee the balance between HBSMs and FBSMs can be calculated in a similar manner to that for the previous method CLC-I. However, due to the asymmetry between  $i_x^U$  and  $i_x^L$ , it is necessary to compute the minimum  $i_q^{\Sigma+}$  for the upper and lower arms separately. The general expression obtained for the upper circulating current is shown in (52) (see the Appendix). For the operating point considered previously to derive (29), and  $i_q=0$ , the required circulating currents  $i_{qU}^{\Sigma+}$  and  $i_{qL}^{\Sigma+}$  for the upper and lower arms respectively are:

$$i_{qU}^{\Sigma+}(\theta_U) = \frac{i_d(-0.649351\theta_U - 0.5\sin(\theta_U) + 2.88846)}{\cos(\theta_U) - 0.0183333}$$

$$i_d(-0.649351\theta_L + 0.5\sin(\theta_L) + 3.08257)$$

(35)

$$i_{qL}^{\Sigma+}(\theta_L) = \frac{i_d(-0.649351\theta_L + 0.5\sin(\theta_L) + 3.08257)}{\cos(\theta_L) - 0.226111}$$

(36)

Notice that  $i_{qU}^{\Sigma+}(\theta_U) = 0.5i_q(\theta_D)$  [see (21) and (33)] which is consistent with the fact that the contribution of the reactive current and circulating component in the upper arm current are  $-0.5i_q$  and  $-i_q^{\Sigma+}$  respectively.

To obtain the feed-forward compensation current, a numerical off-line minimisation procedure is used to calculate the angles  $\theta_U$  and  $\theta_L$  that minimise  $i_{qU}^{\Sigma+}$  and  $i_{qL}^{\Sigma+}$  respectively. The optimisation problem is almost identical to that depicted in (30), but using circulating currents instead of imposing a reactive current component in the grid. For the same operating point, the maximum of the pair  $(i_{qU}^{\Sigma+}, i_{qL}^{\Sigma+})$  is used as the feed-forward compensating current and is stored in a look-up table. This is shown in Fig. 5(c).

## C. ADVANTAGES AND DISADVANTAGES OF CLC-I AND CLC-II

A comparison of the advantages and disadvantages of circulating/reactive currents for capacitor voltage balancing in a hybrid MMC has not been presented in the literature before and it is fully analysed in this section.

The main differences between CLC-I and CLC-II are the modulation margin and the power factor of the grid currents. The modulation margin is the unoccupied sub-module capacitor voltage per arm. When reactive current is utilised (see Section IV.A), it is relatively simple to demonstrate [from (5)]

that the reactive current in steady state is:

$$0 = v_d^{\Delta} + 2V_g - \omega_g L i_q \rightarrow i_q = \frac{v_d^{\Delta} + 2V_g}{\omega_g L}$$

(37)

where the variables are oriented along the grid voltage,  $\omega_g$  is the grid angular frequency,  $V_g$  is the grid voltage,  $v_d^\Delta$  is the d-axis voltage synthesised by the hybrid-MMC and L is the arm inductance. From (37) it is concluded that in steady state operation when  $i_q=0$ ,  $v_d^\Delta$  is intrinsically negative with a value of  $v_d^\Delta\approx -2V_g$ . Therefore (37) can be written as:

$$i_q = \frac{V_g - (|v_d^{\Delta}|/2)}{\omega_g(L/2)}$$

(38)

where the voltage  $|v_d^{\Delta}|/2$  is equivalent to a "converter voltage" (see [28]). Using (38), it is concluded that the magnitude of  $i_q$ , when the hybrid-MMC is supplying a lagging reactive power to the grid  $(i_q > 0)$ , is simple to increase by reducing the voltage  $|v_d^{\Delta}|$  synthesised by the converter. Therefore there is a relatively large voltage (the full magnitude of the grid voltage vector) to produce this current. On the other hand, if it is required to supply leading reactive power to the grid (i.e.  $i_q < 0$ ), the voltage  $|v_d^{\Delta}|$  synthesised by the converter has to be increased until the numerator of (38) becomes negative. Therefore, if the voltage margin in the capacitors is low, particularly in the time interval where only the FBSMs (e.g. for m > 2) are operating, then it is concluded that there is less voltage margin available, i.e. without reaching overmodulation, to achieve operation with  $i_q < 0$ . Moreover, if the hybrid MMC is connected to a weak grid with a non-negligible Thevenin reactance, a larger value of  $|v_d^{\Delta}|/2$ is required to regulate a reactive current  $i_q < 0$ .

In summary, regarding CLC-I, it can be concluded that the main advantage of this strategy (for  $i_q>0$ ) is the relatively large voltage margin available which can be used to improve the dynamic response and steady state operation of this method. This is further corroborated by the experimental results depicted in Section VI. The main disadvantage of CLC-I is that the grid has to operate with low power factor, and this could be infeasible for long-term operation.

To analyse CLC-II, the arm voltage  $v_a^U$  obtained from (3), is used:

$$v_a^U = v_\alpha^{\Sigma} + v_0^{\Sigma} + \frac{1}{2}v_\alpha^{\Delta} + \frac{1}{2}v_0^{\Delta}$$

(39)

Using (5) and neglecting the voltage drop in the inductance, the values of  $v_0^{\Sigma}$ ,  $v_{\alpha}^{\Delta}$  and  $v_0^{\Delta}$  can be replaced by their equivalents in natural coordinates as:

$$v_a^U \approx v_\alpha^\Sigma + \frac{E}{2} + v_{ga} + v_0 \tag{40}$$

where the voltage  $v_{ga}$  is the phase-a grid voltage, E is the dc-link voltage and  $v_0$  is the common mode voltage, which is not considered in this application (i.e. $v_0 = 0$ ). Therefore the upper arm has to synthesise a peak  $v_a^U$  value approximately equal to the sum of the peak phase to neutral grid voltage, half of the dc-link voltage and the peak value of  $v_\alpha^\Sigma$ .

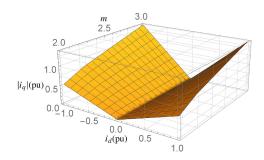

**FIGURE 3.** Minimum  $|i_q|$  (pu) as a function of the modulation index m and the direct current  $i_d$  (pu).

Considering that a fraction of the voltage  $v_{\alpha\beta}^{\Sigma}$  is required to regulate the current  $i_q^{\Sigma+}$ , utilised in CLC-II, the voltage margin (at a particular operating point) is provided by the maximum value of  $|v_{\alpha\beta}^{\Sigma}|$  that can be synthesised without over-modulation resulting in in any of the submodules. However, it is not simple to determine this margin considering that the components of the circulating current required for balancing the energy in the hybrid-MMC [see (13)] are also regulated using  $v_{\alpha\beta}^{\Sigma}$ . Using the criterion reported in [29] the fraction of the capacitor voltage utilised for  $v_{\alpha}^{\Sigma}$  could be set to  $\approx 20\%$  (for an HVDC system). However this 20% of voltage margin is still well below that available in CLC-I when  $i_q > 0$  [see (38)].

In summary, the strategy CLC-II has less voltage margin than that of CLC-I (for  $i_q > 0$ ) and this affects the dynamic performance of this methodology and the maximum value of  $i_q^{\Sigma+}$  which can be synthesised. However, the main advantage of this control methodology is that the grid can be operated with unity power factor.

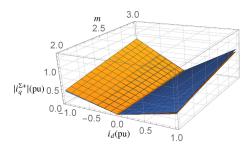

The optimal values of the reactive current  $i_q$  (CLC-I) and circulating current  $i_q^{\Sigma+}$  that guarantee the local balance between the HBSMs and FBSMs are shown in Figs. 3 and 4 respectively. These values have been obtained using the methodology discussed in Section IV. Notice that for determining Fig. 4 unity power factor operation at the grid side has been considered. The compensating currents required ( $i_q$ and  $i_q^{\Sigma+}$ ) are shown as a function of the modulation index m and the direct grid-current  $i_d$ . In both cases, the required current increases as the modulation index or the direct current increases. Moreover, it has to be considered that the current  $|i_q|$  is a grid current and the current  $|i_q^{\Sigma+}|$  is the arm current. Therefore their magnitudes cannot be directly compared unless it is considered that the arm current produced by CLC-I is half of  $|i_q|$  [see (21)]. Finally notice that the absolute values, i.e.  $|i_q|$  and  $|i_q^{\Sigma+}|$ , are shown in Figs. 3 and 4 because equal balancing performance is obtained with  $\pm i_q$  and  $\pm i_q^{\Sigma+}$ . As stated in Section IV.B, for CLC-II the optimisation problem has to be solved for the upper and lower arms independently. The currents for the upper and lower arms are shown in the yellow and blue plots of Fig. 4. For  $i_d > 0$  ( $i_d < 0$ ), the magnitude of the required current for the lower arms is higher (lower) than that of the upper arms.

**FIGURE 4.** Minimum  $|i_g^{T+}|$  (pu) as a function of the modulation index m and the direct current  $i_d$  (pu).

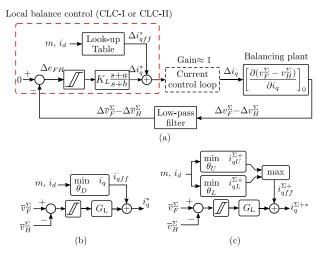

FIGURE 5. Proposed local balance control. (a) general structure of the local balance control, (b) proposed control CLC-I, and (c) proposed control CLC-II

### **V. LOCAL CAPACITOR VOLTAGE CONTROL**

The local capacitor voltages of the FBSMs and HBSMs when the arm current becomes unipolar. The local balance control is shown in Fig. 5. In Fig. 5(a) the outer control loop is shown, as well as a feed-forward current component stored in a look-up table. This feed-forward component could be obtained either from the CLC-I strategy [see Fig. 5(b)] or from the CLC-II control strategy [see Fig. 5(c)]. The design of the outer control loop is discussed below in Section V-A.

## A. DESIGN OF THE OUTER VOLTAGE CONTROL LOOP

As shown in Fig. 5(a), the voltage difference  $e_{FH}$  between the average capacitor voltages of the FBSMs ( $v_{CF}^{\Sigma}$ ) and the HBSMs ( $v_{CH}^{\Sigma}$ ) [see (18)-(20)] is filtered out and processed by a controller based on a lag network which can be designed to have a high rejection of the dc component of the error  $e_{FH}$ . An integrator is avoided in this application because, in steady state operation, the average capacitor voltages of the FBSMs and HBSMs could be slightly different even when the energies in the FBSMs and HBSMs are balanced. Therefore, the utilisation of a PI controller is not a suitable option to regulate  $\Delta e_{FH}$ .

For the design of the lag controller it is assumed that a slow dynamic is required for the outer voltage control loop, considering that a well-estimated feed-forward compensating

FIGURE 6. Gain of the local balance plant for CLC-I.

current will compensate most of the error  $e_{FH}$  with the faster dynamic response typically produced by the inner control loops. Therefore, the transfer function between  $\Delta i_q^*$  and  $\Delta v_{CF}^{\Sigma} - \Delta v_{CH}^{\Sigma}$  can be represented as a small signal gain evaluated in a quiescent point "0", i.e:

$$\Delta e_{FH} = \left[ \frac{\partial \left( v_{CF}^{\Sigma} - v_{CH}^{\Sigma} \right)}{\partial i_q} \right]_0 \Delta i_q = K_{FH} \Delta i_q \qquad (41)$$

A similar transfer function to that depicted in (41) can be obtained for the CLC-II strategy. A voltage hysteresis band is utilised in the outer control loop, therefore if  $e_{FH}$  is greater than the upper threshold,  $V_{CU}$ , then the lag compensator is activated, and will be deactivated when  $e_{FH}$  is below the lower threshold  $V_{CL}$ . The transfer function of the lag-controller is:

$$G_L = K_L \frac{s+a}{s+b} \tag{42}$$

The dc-gain of the lag controller depicted in (42) is equal to  $(a/b)K_L$ . Therefore by adequately selecting the values of  $K_L$ , a and b a good rejection of the dc-component of  $e_{FH}$  is obtained. In this work the design of the lag controller has been realised using the root locus method. The gain  $K_{FH}$  of (41) has been obtained using simulation work considering different modulation indexes, for a hybrid MMC with  $N_F/N_H=1/2$ . The results are obtained in Fig. 6 and they are very similar for both the CLC-I and CLC-II strategies. In Fig. 6(a) the variation of the  $e_{FH}$  respect to the reactive current is shown, the voltage error is expressed in per unit

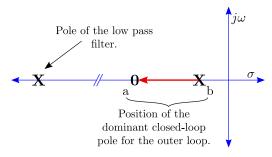

FIGURE 7. Root locus for the design of the outer control loop.

and the base voltage is defined as the total capacitor voltage reference  $Nv_C^*$ . Notice that after the balancing is achieved, increasing the current  $i_q$  (or  $i_q^{\Sigma+}$ ) does not produce any effect in the error  $e_{FH}$ .

The small signal gain  $K_{FH}$  [see (41)] is shown in Fig. 6(b). Using m=2.2 as an example, it is shown in Fig. 6(b) that for an  $i_q$  current below  $\approx 0.15$ pu the gain  $K_{FH}$  is  $\approx 0$ . This is because the arm current is unipolar and no balancing is possible. For  $i_q > 0.15$ pu the gain  $K_{FH}$  is strongly non-linear until it returns to zero when the balancing is achieved. Notice that after balancing the energy between the full and half bridge cells in the converter, the effects produced in  $e_{FH}$  by increasing the current  $i_q$  (or  $i_q^{\Sigma+}$ ) are negligible. The gain  $K_{FH}$  has units of Ohms and consequently is expressed in per unit considering the base impedance.

Using Fig. 6 the design of the lag controller [see (42)] is simple to realise using Root Locus or any other control-design methodology. From Fig. 5(a) it is concluded that the outer voltage control system has a closed loop transfer function with a single dominant pole whose location is between the zero "a" and the pole "b" (see Fig. 7). Therefore, the natural frequency of this dominant pole is limited. Moreover, even when the variation of the gain  $K_{FH}$  could be relatively high, as shown in Fig. 6, this gain variation is restricted when the feedforward compensating currents of CLC-I and CLC-II are relatively well estimated. Therefore a good design of the lag controller is relatively simple to realise.

To show the effects of using relatively well- estimated feedforward compensating currents in the gain variation of  $K_{FH}$ , an example is provided considering m=2.8 operation. With a good estimation of these currents the gain  $K_{FH}$  is approximately confined to the limits of the dashed-box located at the right of Fig. 6(b).

#### B. IMPLEMENTATION OF THE INNER CONTROL LOOPS

The control diagram for CLC-I is depicted in Figs. 5b. A look-up table is used to determine the feed-forward reactive current  $i_{qff}$  obtained by applying the optimising procedure discussed in Section IV-A [see (30)]. The total reactive current reference  $i_q^*$ , obtained by adding the outputs of the lag controller and the look-up table, is regulated by the current control loops of the overall control system (see bottom right side of Fig. 8).

The control diagram for the CLC-II strategy discussed in Section IV-B is shown on Fig. 5c. The main difference with CLC-I is that the required optimal circulating current  $i_q^{\Sigma+}$  is different for the upper  $(i_{qU}^{\Sigma+})$  and lower  $(i_{Lq}^{\Sigma+})$  arms. Therefore, to ensure a good balance of both arms, the maximum value of the two currents (i.e. upper and lower arms) is considered. The total current  $i_q^{\Sigma+*}$ , obtained as the sum of the lag controller output and look-up table (maximum) output, is regulated by the current control loops of the overall balancing control system (see bottom left side, below the green box of Fig. 8).

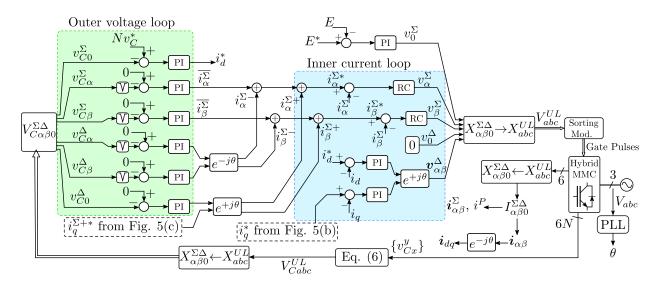

#### VI. GLOBAL CAPACITOR VOLTAGE CONTROL

The global capacitor voltage control shown in Fig. 8 ensures balancing of the total energy among the six arms. It is composed of an outer voltage layer (green) and an inner current layer (blue). The floating capacitor voltages within each arm are added to obtain the total capacitor voltage  $V_{Cabc}^{UL}$  which is then referred to the  $\Sigma\Delta\alpha\beta0$  reference frame. Notice that the term  $v_{C\alpha\beta}^{\Sigma}$  has a double frequency component  $2\omega_g$  due to the term  $0.25(v_{\alpha\beta}i_{\alpha\beta})^c$  [see (10)], while the term  $v_{C\alpha\beta}^{\Delta}$  has a frequency component  $\omega_g$  (11). The oscillatory components of  $v_{C\alpha\beta}^{\Sigma}$  and  $v_{C\alpha\beta}^{\Delta}$  are removed using notch filters tuned at  $2\omega_g$  and  $\omega_g$  respectively. To ensure the balance among the 6 arms, the voltage references in the  $\Sigma\Delta\alpha\beta0$  coordinate frame are:

$$v_{C0}^{\Sigma*} = Nv_C^* \quad v_{C\alpha}^{\Sigma*} = v_{C\beta}^{\Sigma*} = v_{C\alpha}^{\Delta*} = v_{C\beta}^{\Delta*} = v_{C0}^{\Delta*} = 0$$

(43)

To regulate the capacitor voltages  $V_{C\alpha\beta0}^{\Sigma\Delta}$ , with zero steady-state error, PI controllers are utilised. The outer voltage controllers provide the circulating current  $i_{\alpha\beta}^{\Sigma*}$ , and grid currents  $i_{dq}^{*}$  to the inner control loops. The circulating currents  $i_{\alpha\beta}^{\Sigma}$  are regulated using proportional resonant controllers tuned at  $\omega_g$  (see [30], [31]). The grid currents  $i_{dq}$  are regulated using PI controllers.

The output of the inner current controllers provide the voltages references  $V_{\alpha\beta0}^{\Sigma\Delta}$  to be synthesised by the hybrid-MMC cells. The arm voltage references  $V_{abc}^{UL}$  are calculated using the inverse  $\Sigma\Delta\alpha\beta0$  transformation. Finally, a sorting modulator is used to generate the gate drive signals for each cell [32]. The sorting modulation algorithm also provides cell-balancing capability within each arm.

#### **VII. EXPERIMENTAL RESULTS**

To validate the proposed control strategies, an experimental prototype of a 5kW-hybrid MMC composed of 18 sub-modules was designed and implemented (see Fig. 9). The parameters of the experimental system are listed in Table 1. The controller was programmed in a DSP Texas Instrument model TMS320C6713 platform augmented by 3 FPGA (Actel) boards (shown at the bottom right of Fig. 10). These boards are used to interface the A/D converters, to implement the hardware protection system (overcurrents and overvoltages), and to generate the pulse-width modulation signals (PWM) of each cell. The grid is emulated using a chroma 61511 programmable supply (shown at the

FIGURE 8. Proposed global balance control.

FIGURE 9. Circuit diagram of the experimental MMC prototype composed of one FBSM and 2 HBSMs in each arm.

**TABLE 1. Parameters of the experimental setup.**

| Parameter | Description                             | Value              |

|-----------|-----------------------------------------|--------------------|

| $N_H$     | HBSMs (IGBT (F4-50R06W1E3/ 50A) per arm | 2                  |

| $N_F$     | FBSMs (IGBT (F4-50R06W1E3/ 50A) per arm | 1                  |

| 6N        | Total number of cells                   | 18                 |

| $V_g$     | Magnitude of the grid voltage           | 120V               |

| $v_C^*$   | Sub-module voltage reference            | 100V               |

| $f_c$     | Carrier frequency (PD-PWM modulation)   | 8kHz               |

| L         | Arm inductance                          | $4.15~\mathrm{mH}$ |

| C         | Cell capacitor (B43564-D4338-M/ 350V)   | 3.3  mF            |

| $R_1$     | Resistive load                          | $11~\Omega$        |

| $R_2$     | Resistive load                          | $22\Omega$         |

bottom left of Fig. 10) and the load is composed of resistors connected to the dc-port side of the hybrid MMC (see Fig. 9).

The entire control algorithms for the CLC-I and CLC-II cases require processing times of  $60.7\mu s$  and  $64.2\mu s$  respectively. The sampling period is  $125\mu s$  (carrier frequency of 8kHz). See Table 1 for further details.

Hybrid MMC (18 cells)

Power supply Chroma 61511

FIGURE 10. Experimental System. At the top are the 18 FBSM and HBSM modules. Bottom left is the Chroma 61511 programmable power supply. Bottom right is the control platform.

# A. OPERATION OF AN UNCOMPENSATED HYBRID MMC IN THE OVER-MODULATION RANGE

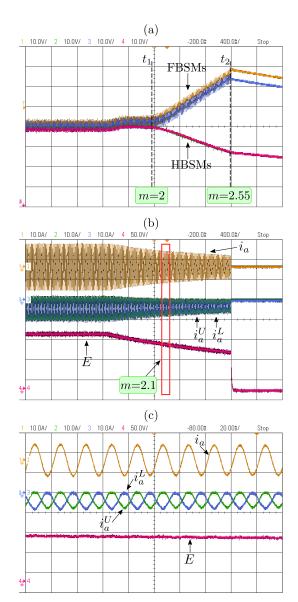

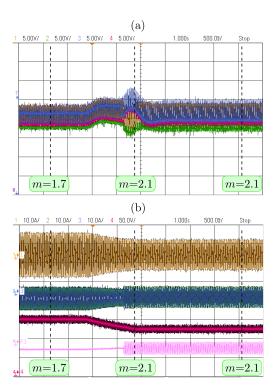

As explained in Section III, when a hybrid MMC operates in over-modulation (m > 2), the arm currents may become unipolar if neither of the control systems depicted in Fig. 5 is enabled. This is experimentally demonstrated in Fig. 11. In this case the hybrid MMC is feeding a resistive load  $R_1 = 11~\Omega$  at the dc-port side (see Fig. 9). Initially, the hybrid MMC operates with a modulation index m = 1.7 equivalent to E = 141V and then the modulation index is ramped from m = 1.7 to m = 2.55 (i.e.  $E \approx 94V$ ).

Fig. 11(a) shows waveforms for the capacitor voltages of the upper arm  $v_{Ca1}^U$  (FBSM, yellow) and  $v_{Ca2}^U$  (HBSM, green), and those of the lower arm are  $v_{Ca1}^L$  (FBSM, blue) and  $v_{Ca2}^L$  (HBSM, red) for phase a. In addition, the grid current  $i_a$ , the arm currents  $i_a^U$  (upper) and  $i_a^L$  (lower), and the dc-port voltage E are shown in the scope waveforms in Fig. 11(b).

**FIGURE 11.** (a) Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red); (b) grid current  $i_a$  (yellow), arm currents  $i_a^U$  (green) and  $i_a^U$  (blue), and dc-port voltage E (red); (c) zoomed view of (b).

An zoomed view of this figure is shown in Fig. 11(c) expanding the zone where the arm currents become negative. After  $t_1$ , the modulation index is m>2 and, as a consequence, the arm currents become unipolar and the capacitor voltages of the FBSMs and HBSMs start to unbalance. At  $t_2$ , the modulation index is m=2.55, and the FBSMs trigger the over-voltage protection  $V_{\rm max}=140{\rm V}$  and the converter is shut down. Notice that for m>2, the capacitor voltages of the FBSMs increase while those of the HBSMs decrease.

# B. OPERATION OF THE PROPOSED CONTROL SYSTEM (CLC-I) FOR OVER-MODULATION OPERATION

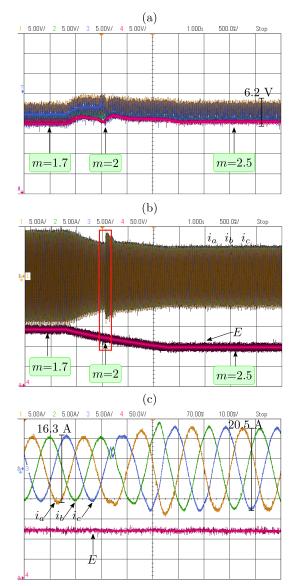

In this section the operation of the control system labelled as CLC-I, discussed in Section IV and depicted in Fig. 5(b), is presented. The currents and voltages produced by the

converter when the modulation index is ramped from m =1.7 to m = 2.5 are shown in Fig. 12. As explained previously, the minimum reactive current to ensure the local balance between FBSMs and HBSMs is derived by solving the optimization problem (30) along with the action of the lag compensator [see Fig. 5]. Fig. 12(a) shows the cell capacitor voltages  $v_{Ca1}^U$  (FBSM, yellow),  $v_{Ca2}^U$  (HBSM, green),  $v_{Ca1}^L$  (FBSM, blue), and  $v_{Ca2}^L$  (HBSM, red). Notice that the FBSMs and HBSMs remain balanced during the whole modulation index sweep. The grid currents and dc-port voltage are shown in Fig. 12(b) with the grid current reaching a peak-to-peak value of  $\approx$ 22.9A at the beginning of the test and a final value of  $\approx$ 14.7A at the end of the test. Notice that the grid current is increased by the CLC-I strategy when m > 2. This is because reactive current is added to the grid current in order to produce a bipolar current in the arms. A zoomed view, when m = 2, is shown in Fig. 12(c). Once m = 2.5, the magnitude of the reactive current is  $i_q \approx 5.1$ A and the power factor is 0.7. In steady-state, the capacitor voltage oscillations are less than 6.2V.

# C. PERFORMANCE COMPARISON BETWEEN CLC-I AND SIMILAR STRATEGIES PREVIOUSLY DISCUSSED IN THE LITERATURE

In [21], [33] among other works, the imbalance problem is also addressed by manipulating the reactive component of the grid currents, but without including the external voltage control loop shown in the nested control system shown in Fig. 5. In the previous publications, it is claimed that the power factor to ensure bipolar arm currents is given by:

$$m\cos(\varphi) < 2$$

(44)

From (44), the reactive current (for m>2) is:

$$\frac{\sqrt{m^2 - 4}}{2} |i_d| \le |i_q| \tag{45}$$

Notice that this expression only guarantees the change of sign of the arm currents. However, it does not necessarily ensure capacitor voltage balance among FBSMs and HBSMs. In addition, (45) only gives a lower bound for the reactive current magnitude. Therefore, a scaling factor has to be included in order to ensure capacitor voltage balance for the whole operating range of the modulation index. Consequently, (45) is rewritten as:

$$i_q = \alpha_1 \frac{\sqrt{m^2 - 4}}{2} |i_d| \tag{46}$$

Since there is no explicit expression given to calculate the required  $i_q^*$  (46), such as the one discussed in this work (see Section IV-A), the minimum reactive current (i.e.  $\alpha_1$ ) has to be obtained using simulation work and/or a methodology based on trial and error. In order to demonstrate the potential difficulties of this approach, a test was conducted on the experimental prototype. Following several iterations of simulation and experimental tests and the use of trail and error, it was determined that  $\alpha_1 = 1.33$  ensures capacitor

**FIGURE 12.** Capacitor voltage balance using CLC-I for  $m=1.7 \rightarrow 2.5$ . (a) capacitor voltages of  $v^U_{Ca1}$  (yellow),  $v^U_{Ca2}$  (green),  $v^L_{Ca1}$  (blue), and  $v^L_{Ca2}$  (red); (b) grid currents  $i_{abc}$  and dc-port voltage E; and (c) zoomed view of the (b).

voltage balance between the FBSMs and the HBSMs for m=2.5. However,  $\alpha_1=1.33$  does not ensure capacitor voltage balance for lower modulation indexes. In Fig. 13(a)-(b), the modulation index reference is changed from m=1.7 to m=2.5 and, although the capacitor voltages are balanced once m=2.5, they drift apart for m=2.1 as shown in Fig. 13(b). If the modulation index is ramped from m=1.7 to m=2.1, the capacitor voltages remain unbalanced as shown in Fig. 13(c) with a capacitor voltage error of  $\approx 7$ V. This problem is produced by the non-linearities of the system (see Fig. 6), and the non-linearities of the term  $\sqrt{m^2-4}$  given in (46). Conversely, with the proposed CLC-I strategy, this problem is not apparent [see Fig. 12(a)]. This is because the minimum current to balance the capacitor voltage is obtained using an explicit expression (see Section IV-A), and

**FIGURE 13.** (a) Grid current  $i_a$  (yellow), Arm currents  $i_a^U$  (green) and  $i_a^L$  (blue), dc-port voltage E (red). Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red) when (a)  $m=1.7 \rightarrow 2.5$  and (b)  $m=1.7 \rightarrow 2.1$ .

the external voltage control loop, depicted in Fig. 5, ensures regulation even if the reactive current is slightly in error.

# D. OPERATION OF THE PROPOSED CONTROL SYSTEM (CLC-II) FOR OVER-MODULATION OPERATION

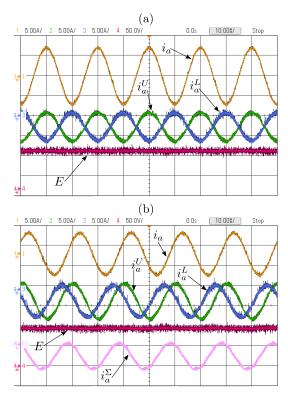

The same modulation index variation  $(m=1.7\rightarrow2.5)$  considered in the experimental results presented in Fig. 12 is repeated but using the CLC-II strategy. In this case, the circulating current component  $i_q^{\Sigma+}$ , obtained using the methodology discussed in Section IV-B, is utilised to balance the FBSMs and HBSMs during over-modulation (m>2).

Fig. 14(a) shows the capacitor voltages  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red). As shown in Fig. 14, at the beginning of the test the grid current (peak-to-peak) is  $\approx$ 22.9A (similar to that depicted in Fig. 12) while at the end it is  $\approx$ 11.2A; this is less than the value obtained for the CLC-I

**FIGURE 14.** (a) Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red). (b) Grid current  $i_a$  (yellow), arm currents  $i_a^U$  (green) and  $i_a^L$  (yellow), dc-port voltage E (red), and circulating current  $i_a^\Sigma$  (pink). (c) zoomed view of (b) when m=2.

case which was ≈14.7A. As discussed previously, the difference in magnitude is produced because the CLC-I strategy uses reactive grid-current to balance the HBSM-FBSM capacitor voltages.

In Fig. 14, circulating current is applied to the arm currents to balance the capacitor voltages. For m>2 a current  $i_q^{\Sigma+}$  is injected, [see lower waveforms of Fig. 14(b) and (c)], with a peak-to-peak value of  $\approx 7.5$ A. Notice that there is a small voltage difference increase  $\approx 3$ V for  $m\approx 2.1$  between the capacitor voltages of the upper and lower arms which becomes negligible after 0.15s. The maximum steady state voltage oscillation is 8.3V. A zoomed view of the grid current  $i_a$ , the arm currents  $i_a^U$  and  $i_a^L$ , the dc-port voltage E, and the circulating current  $i_a^\Sigma$  are shown in Fig. 14(c) for the zone where  $m\approx 2$ .

**FIGURE 15.** (a) Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red). (b) Grid current  $i_a$  (yellow), arm currents  $i_a^U$  (green) and  $i_a^L$  (yellow), dc-port voltage E (red), and circulating current  $i_a^\Sigma$  (pink).

As mentioned before, when CLC-II is applied, there is a reduced unbalance of  $\approx$ 3V between the average voltages of the upper and lower arm. However, this variation is not permanent even if the system operates at  $m \approx 2.1$  in steady state. To experimentally verify this, a ramp variation in the modulation index between m=1.7 to m=2.1 is realised. These results are shown in Fig. 15. Notice that the capacitor voltages  $v_{Ca1}^U$ ,  $v_{Ca2}^U$ ,  $v_{Ca1}^L$ , and  $v_{Ca2}^L$  remain balanced during the whole test as depicted in Fig. 15(a) with a capacitor voltage oscillation of  $\approx$ 7.8V in steady state. The grid current  $i_a$  (yellow), arm currents  $i_a^U$  (green) and  $i_a^L$  (yellow), dc-port voltage E (red), and circulating current  $i_a^2$  (pink) are shown in Fig. 15(b).

# E. PERFORMANCE COMPARISON BETWEEN CLC-II AND SIMILAR STRATEGIES PREVIOUSLY DISCUSSED IN THE LITERATURE

In [9], [23], among other works, the utilisation of circulating current to avoid imbalance problems between the capacitor voltages of the HBSMs and FBSMs, during over-modulation operation, is reported. Again an external voltage control loop was not considered in this previous work and a rigorous mathematical methodology to minimise the required circulating currents was neither proposed nor discussed. In [9], the injected reactive current is calculated to ensure the bipolarity of the arm current. This is achieved using:

$$|i_q^{\Sigma+}| \ge \frac{i_d}{4} \sqrt{m^2 - 4} \tag{47}$$

However, the current required to balance the capacitor voltages of the HBSMs and FBSMs is not necessarily equal to the minimum current required to achieved bipolarity. To ensure balancing for  $m \approx 2.5$ , (47) has to be multiplied by a constant  $\alpha_2 > 1$  yielding:

$$i_q^{\Sigma +} = \alpha_2 \frac{i_d}{4} \sqrt{m^2 - 4} \tag{48}$$

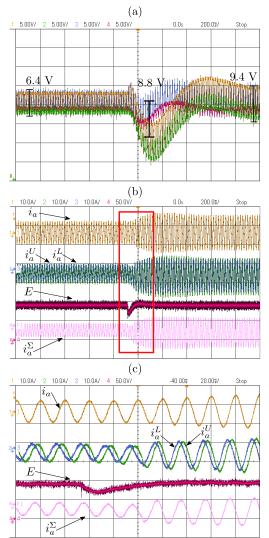

Similarly to the reactive current case discussed in Section VII-C, an explicit equation to calculate the value of  $\alpha_2$  which ensures the balance between the FBSMs and HBSMs was not given. Therefore, again, the value has to be obtained using simulation and/or experimental work combined with some heuristic procedures. Using this approach for the experimental prototype, the value that ensures capacitor voltage balancing for  $m \approx 2.5$  is  $\alpha_2 = 1.65$ . Again, considering the strong non-linearities of the system [see Fig. 6 and (48)], this value is not necessarily appropriate for operating in steady state with smaller value of m.

To demonstrate the potential problems, Fig. 16(a)-(b) show the performance of the control strategy implied by (48), when the modulation index is changed from m=1.7 to m=2.5 and the required circulating current is calculated using (48) with  $\alpha_2=1.65$ . The grid current  $i_a$ , arm currents  $i_a^U$  and  $i_a^L$ , and the dc-port voltage E are also shown in Fig. 16(a). The capacitor voltages  $v_{Ca1}^U$  (FBSM, yellow),  $v_{Ca2}^U$  (HBSM, green),  $v_{Ca1}^L$  (FBSM, blue), and  $v_{Ca2}^L$  (HBSM, red) are shown in Fig. 16(b). Notice that for m<2.5 the capacitor voltages are unbalanced. If the modulation index reference is ramped from  $m=1.7\rightarrow2.1$  the capacitor voltages remain unbalanced as shown in Fig. 16(c). In this case, the capacitor voltage error is  $\approx15$ V which is a relatively large error considering that the nominal voltage of each submodule is 100V.

As demonstrated in Sections VII-C and VII-E, a single value of  $\alpha_{1,2}$  in either (46) or (48) is not adequate to achieve capacitor voltage balancing between the HBSMs and FBSMs in the entire over-modulation range, particularly if the aim is to minimise the reactive or circulating currents which are required in the Hybrid MMC. Therefore, several values of  $\alpha_{1,2}$  could be required to achieve good performance in a wide operating range. Moreover, extensive experimental and simulation work could be required to implement the previously reported approaches. Conversely, in the control systems proposed here, the explicit equations [see (49)-(52)] presented in the Appendix, can be used to minimise the required reactive or circulating current which is necessary to balance the HBSM-FBSM capacitor voltage for operating the hybrid MMC with any value of m. Moreover, there is an additional outer voltage control loop layer in the proposed approach. This additional loop [see Fig. 5(a)] is activated when the capacitor voltage balancing error  $v_{CF}^{\Sigma} - v_{CH}^{\Sigma}$  is larger than a predefined hysteresis band.

**FIGURE 16.** (a) Grid current  $i_a$  (yellow), Arm currents  $i_a^U$  (green) and  $i_a^L$  (blue), dc-port voltage E (red), and circulating current  $i_a^\Sigma$  (pink). Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red) when (a)  $m=1.7 \rightarrow 2.5$  and (b)  $m=1.7 \rightarrow 2.1$ .

# F. DYNAMIC AND STEADY STATE PERFORMANCE OF THE OUTER CONTROL LOOP

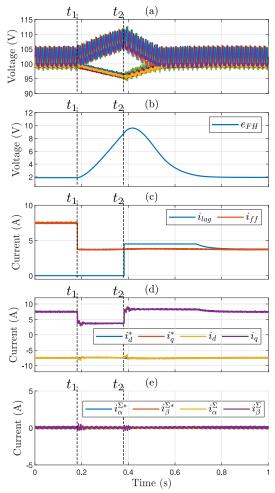

This work proposes the use of a new outer voltage control loop layer to ensure the capacitor voltage balance between the HBSMs and FBSMs even if the feedforward currents have errors. This loop is depicted in Fig. 5(a) and is based on a lag compensator designed using the methodology discussed in Section V-A and Fig. 7.

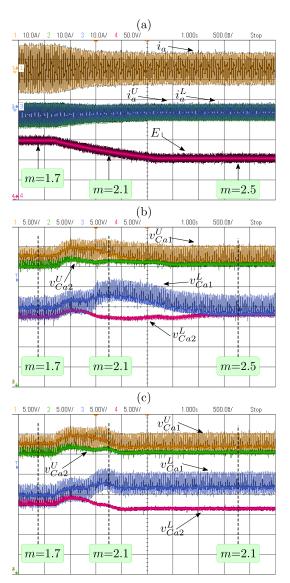

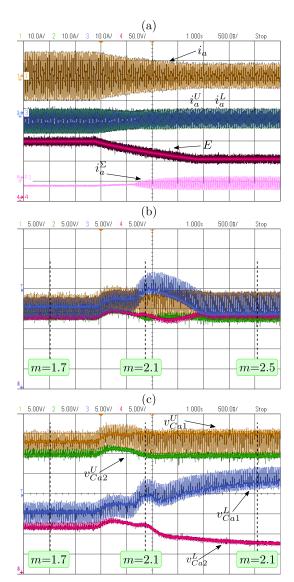

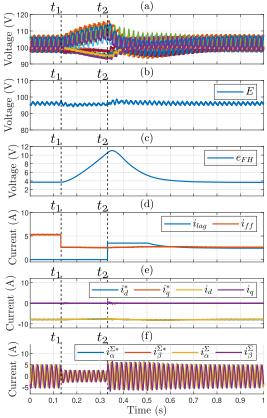

In the following results, to check the performance of the lag compensator, an error is intentionally introduced in the feed-forward compensating current using a step change to reduce it to 50% of its correct value. Subsequently, after 200ms has elapsed, the lag compensator is activated to regulate the capacitor voltage error  $e_{FH}$  between the FBSMs and the HBSMs. During the test the hybrid MMC operates in the

**FIGURE 17.** Lag operation using CLC-I:(a) cell capacitor voltages, (b) voltage error  $e_{FH}$  between the FBSMs and the HBSMs, (c) feed-forward current and lag current, (d) grid currents  $i_{dq}$  and  $i_{dq'}^*$ , and (e) circulating currents  $i_{\alpha\beta}^*$  and  $i_{\alpha\beta}^{\Sigma*}$ .

over-modulation range with m = 2.5 (E = 96V) and it feeds a load  $R_L = 7.3$   $\Omega$  connected at the dc-side port.

In Fig. 17 some internal variables utilised by the CLC-I algorithm implemented in the control platform (e.g.  $i_d$  and  $i_a$ ) are obtained from the data acquisition system of the DSP. The cell capacitor voltages are shown in Fig. 17(a). The capacitor voltage error between the FBSMs and the HBSMs is shown in Fig. 17(b). Initially  $e_{FH} \approx 1.8$ V but once the feed-forward current is reduced the voltage error increases to  $e_{FH} \approx 9.6$ V. After the lag compensator is activated the voltage error is regulated with a settling time of  $\approx 150$  ms [see Fig. 17(a)]. The feed-forward current  $i_{ff}$  and the output of the lag compensator  $i_{lag}$  are shown in Fig. 17(c). Initially, the magnitude of the feed-forward current is  $\approx$ 7.6A and the output of the lag compensator is zero. At  $t_1$ , a step reduction of  $i_{ff}$  to 3.8A is introduced and, consequently, the error  $e_{FH}$  increases. After the outer control loop is activated at  $t_2$ , the reactive current reference is increased to  $i_q^* = 8.4$ A by the lag compensator before falling back to the initial value  $i_q^* \approx 7.6$ A once  $e_{FH}$  is reduced in steady-state. Notice that the large error introduced artificially into  $i_{ff}$  is completely removed by the lag compen-

**FIGURE 18.** Lag operation using CLC-I: (a) Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red). (b) grid current  $i_a$  (yellow), the arm currents  $i_a^U$  (green) and  $i_a^L$  (blue), and the dc-port voltage E (red). (c) zoomed view of (b) once the lag compensator is activated.

sator. In addition, the grid currents  $i_{dq}$  and their references are shown in Fig. 17(d). Finally, the circulating currents  $i_{\alpha\beta}^{\Sigma}$  and their references are shown in Fig. 17(e) notice that the circulating currents are negligible because the CLC-I strategy is based on manipulating the reactive grid-current.

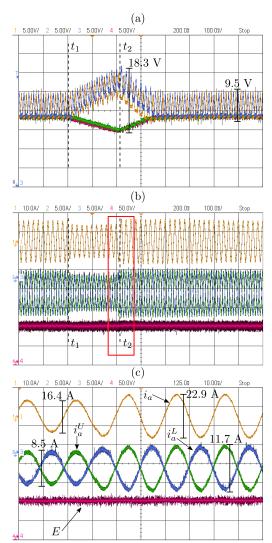

The variables captured by the digital scope, corresponding to the experimental test depicted in Fig. 17 are shown in Fig. 18. The capacitor voltages  $v_{Ca1}^U$  (yellow, FBSM),  $v_{Ca2}^U$  (green, HBSM),  $v_{Ca1}^L$  (blue, FBSM), and  $v_{Ca2}^L$  (red, HBSM) are shown in Fig. 18(a). After the feed-forward current is reduced at  $t_1$ , the capacitor voltages of the FBSMs increase, while for the HBSMs the voltages decrease. The maximum voltage difference is 18.3V but, in steady state, after the outer control loop is enabled the voltage difference is 8.1V. The grid current  $i_a$ , the arm currents  $i_a^U$  and  $i_a^L$ , and the dc-port voltage are shown in Fig. 18(b). A zoomed view of Fig. 18(b) is shown in Fig. 18(c) corresponding to the zone where the lag compensator is activated. Before  $t_2$ , the peak-to-peak

**FIGURE 19.** Lag operation using CLC-II:(a) cell capacitor voltages, (b) voltage error  $e_{FH}$  between the FBSMs and the HBSMs, (c) feed-forward current and lag current, (d) grid currents  $i_{dq}$  and  $i_{dq'}^*$  and (e) circulating currents  $i_{\alpha\beta}^{\Sigma}$  and  $i_{\alpha\beta}^{\Sigma}$ .

grid current is 16.4A which increases to 22.9A once the lag compensator is enabled.

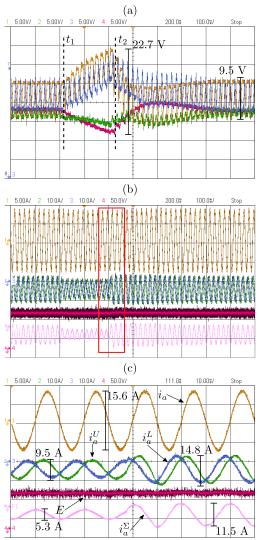

The experimental tests are repeated, using identical conditions, for the CLC-II strategy. Again some of the internal variables (e.g  $i_q^{\Sigma+}$ ) are obtained using the data acquisition system available in the DSP-based control platform. The cell capacitor voltages are shown in Fig. 19(a), the dc-link voltage is shown in Fig. 19(b), and the voltage error is shown in Fig. 19(c). Initially, the capacitor voltage error is  $e_{FH} \approx 3.7 \text{V}$  which increases to  $e_{FH} \approx 11.1 \text{V}$  when the feed-forward current is reduced (by 50%). However, when the outer control loop [shown in Fig. 5(a)] is activated, the voltage error is reduced back to its initial value.

The feed-forward current and the current produced at the output of the lag compensator are depicted in Fig. 19(d). Initially, the feed-forward current is 5.2A and the lag compensator is disabled. At  $t_1$ , the feed-forward current is reduced by  $\approx 50\%$  and the error  $e_{FH}$  increases. After the outer control loop is activated at  $t_2$ , the magnitude of  $i_q^{\Sigma+}$  reaches 6.1A which is again reduced to  $i_q^{\Sigma+}\approx 5.2$ A when the error  $e_{FH}$  achieves steady state. Again, the large error introduced artificially into  $i_{ff}$  is completely removed by the lag compensator. The grid currents  $i_{dq}$  and  $i_{dq}^*$  are shown in Fig. 19(e), notice that the converter operates with unity power factor during the whole test, with  $i_d^*=-7.9$ A (which is one of the advantages of the

CLC-II strategy). Finally, the circulating currents  $i_{\alpha\beta}^{\Sigma}$  and their references are shown in Fig. 19(f). The settling time of the capacitor voltage regulation is  $\approx$ 160ms, as shown in Fig. 19(a) and Fig. 20(a).

The variables captured by the digital scope, corresponding to the experimental test of Fig. 19 are shown in Fig. 20. In this case the capacitor voltages  $v_{Ca1}^U$ ,  $v_{Ca2}^U$ ,  $v_{Ca1}^L$ , and  $v_{Ca2}^L$  are shown in Fig. 20(a). After the feed-forward current is reduced the capacitor voltage difference increases to 22.7V, but once the outer control loop is activated the original conditions are restored. Due to the asymmetry in the charging process between the upper and lower arm cells (see Section IV-B), the upper arm capacitor voltage balancing is faster ( $\Delta t \approx 90$ ms) than that of the lower arm ( $\Delta t \approx 160$  ms). The grid current  $i_a$ , arm currents  $i_a^U$  and  $i_a^L$ , dc-port voltage E, and circulating current  $i_a^{\Sigma}$  are shown in Fig. 20(b), a zoomed view of Fig. 20(b) is shown in Fig. 20(c), corresponding to the zone where the outer control loop is activated. When CLC-II is used the grid current is not affected and the converter operates with unity power factor. The peak-to-peak value of the grid current  $i_a$  is 15.6A.

# G. DYNAMIC RESPONSE OF THE PROPOSED CONTROL STRATEGIES FOR STEP VARIATIONS IN THE LOAD

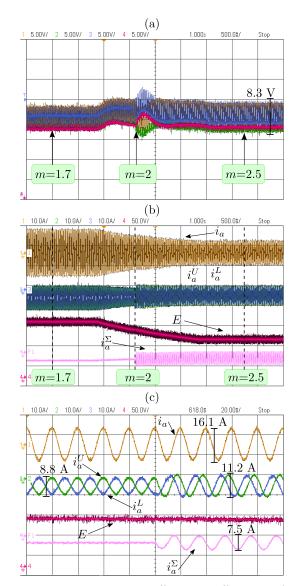

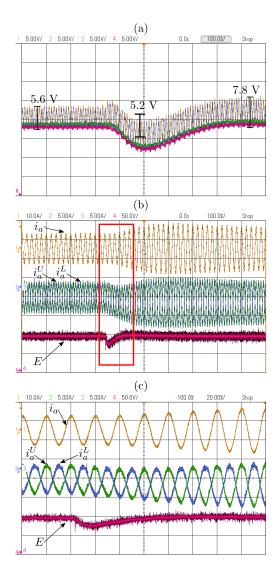

The control performance is tested considering a load impact at the dc-port side. The hybrid MMC is operating with m=2.5 feeding a resistive load  $R_L=11~\Omega$  when an impact load occurs and the load resistance is reduced to  $R_L=7.3~\Omega$ . The performance of both control strategies (CLC-I and CLC-II) is analysed and compared.

Fig. 21 shows the converter variables when CLC-I is used. The capacitor voltages  $v_{Ca1}^U$ ,  $v_{Ca2}^U$ ,  $v_{Ca1}^L$ , and  $v_{Ca2}^L$  are shown in Fig. 21(a). Initially, the capacitor voltage oscillations around the mean value are 5.6V and after the load impact they are slightly increased to 7.8V. During the whole test, the FBSMs and HBSMs remain balanced. Notice that, the average voltage of the upper and lower sub-modules have a dip of about 5.2V, due to the load impact, but the control of  $v_{C0}^{\Sigma}$  [see Fig. 8] is able to regulate the total capacitor voltage of each arm in about 400ms.

The grid current  $i_a$ , arm currents  $i_a^U$  and  $i_a^L$  and the dc-port voltage E are shown in Fig. 21(b) and (c). During the entire test the grid side operates with a power factor of  $\approx$ 0.7 because the CLC-I strategy is being used. The peak-to-peak value of the grid current  $i_a$  is 7.3A before the load impact and increases to 12.7A after the load impact before settling down to  $\approx$ 10.9A in steady state. Immediately following the load impact the dc-port voltage has a dip of  $\approx$ 25V and the control system is able to restore it to the reference value of E = 96V in  $\approx$ 60ms.

The experimental tests are repeated, using identical conditions, for the CLC-II strategy. The experimental results are shown in Fig. 22.

The capacitor voltages  $v_{Ca1}^U$ ,  $v_{Ca2}^U$ ,  $v_{Ca1}^L$ , and  $v_{Ca2}^L$  are shown in Fig. 22(a). Initially, the capacitor voltage oscillations, around the mean value, are 6.4V. After the load impact, the capacitor voltage oscillations are  $\approx 9.4$ V [see the green

**FIGURE 20.** Lag operation using CLC-II: (a) Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red). (b) grid current  $i_a$  (yellow), the arm currents  $i_a^U$  (green) and  $i_a^L$  (blue), and the dc-port voltage E (red). (c) zoomed view of (b) once the lag compensator is activated.

waveform in Fig. 22(a)]. Due to the load impact, the mean capacitor voltages decrease initially by 8.8V before the global capacitor voltage control system regulates them back to the reference value in 450ms. Fig. 22(b) and (c) show the grid current  $i_a$ , arm currents  $i_a^U$  and  $i_a^L$  and the dc-port voltage E. Before the perturbation, the peak value of the circulating current is 3.4A which increases to 7.6A after the load impact.

The main advantage of the CLC-II strategy with respect to CLC-I, is that the converter operates with unity power factor at the grid-side port. However, as discussed in detail in Section IV-C [see also (37)-(38)], the CLC-II strategy has a smaller voltage margin to regulate the circulating currents used in the hybrid-MMC. Therefore its dynamic response is slower than that obtained with the CLC-I strategy (see Fig. 21). This is also confirmed by the response of the control system regulating the dc-link voltage. The dc-port voltage decreases by  $\approx$ 25V and the control system regulates it back to E=96V in  $\approx$ 95ms.

**FIGURE 21.** Impact load using CLC-I: (a) Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red). (b) grid current  $i_a$ , arm currents  $i_a^U$  and  $i_a^L$  and the dc-port voltage E. (c) zoomed view of (b).

# H. STEADY-STATE WAVEFORMS AND CAPACITOR VOLTAGE SPECTRUM FOR THE PROPOSED CONTROL STRATEGIES

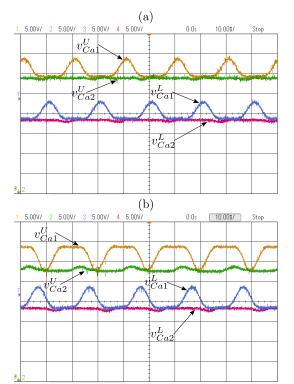

The capacitor voltages  $v_{Ca1}^U$  (FBSM),  $v_{Ca2}^U$  (HBSM),  $v_{Ca1}^L$  (FBSM), and  $v_{Ca2}^L$  (HBSM) in steady-state operation are shown for both control strategies (CLC-I and CLC-II). For this test the converter is operating with a modulation index of m=2.5 and a resistive load of  $11\Omega$  is connected to the dc-link port. The steady state responses for the CLC-I and CLC-II strategies are shown in Figs. 23(a) and (b) respectively.

When CLC-II is used, the charging/discharging behaviour of the sub-modules of the upper and lower arms is no longer symmetric because the arm currents are asymmetric, according to (33)-(34), and this is reflected in the waveforms depicted in Figs. 23(a) and (b). For both strategies, the capacitor voltage ripple is more significant for the FBSMs with peak to peak values of 6.2V and 8.3V for CLC-I and CLC-II respectively. The ripple in the HBSMs is much less because

FIGURE 22. Impact load using CLC-II: (a) Capacitor voltages of  $v_{Ca1}^U$  (yellow),  $v_{Ca2}^U$  (green),  $v_{Ca1}^L$  (blue), and  $v_{Ca2}^L$  (red). (b) grid current  $i_a$ , arm currents  $i_a^U$  and  $i_a^L$  and the dc-port voltage E. (c) zoomed view of (b).

only the FBSMs contribute to the arm voltage when it is negative during over-modulation (the HBSMs are bypassed and produce zero contribution).

The spectra, obtained using the Discrete Fourier Transform (DFT), of the capacitor voltages  $v_{Ca1}^U$  (FBSM) and  $v_{Ca2}^U$  (HBSM) for CLC-I and CLC-II are shown in Fig. 24(a) and (b) respectively where the magnitudes are expressed as a percentage of the fundamental. Since the magnitude of the harmonic components are low (<3%), an expanded view of the spectrum is shown in Fig. 24. Notice that regardless of the strategy, the harmonic components of the FBSM capacitor voltages are greater than those of the HBSMs. For instance, for CLC-I, the second harmonic of  $v_{Ca1}^U$  (FBSM) and  $v_{Ca2}^U$  (HBSM) are 0.8% and 0.1% respectively while, for CLC-II, the second harmonic of  $v_{Ca1}^U$  and  $v_{Ca2}^U$  are 1.2% and 0.2% respectively.

In Fig. 24, The DFTs corresponding to the upper arm capacitor voltages are shown. For CLC-I both the upper and